RF蓝牙BLE模块笔记

- 预学习阶段:接收机和发射机的结构概述

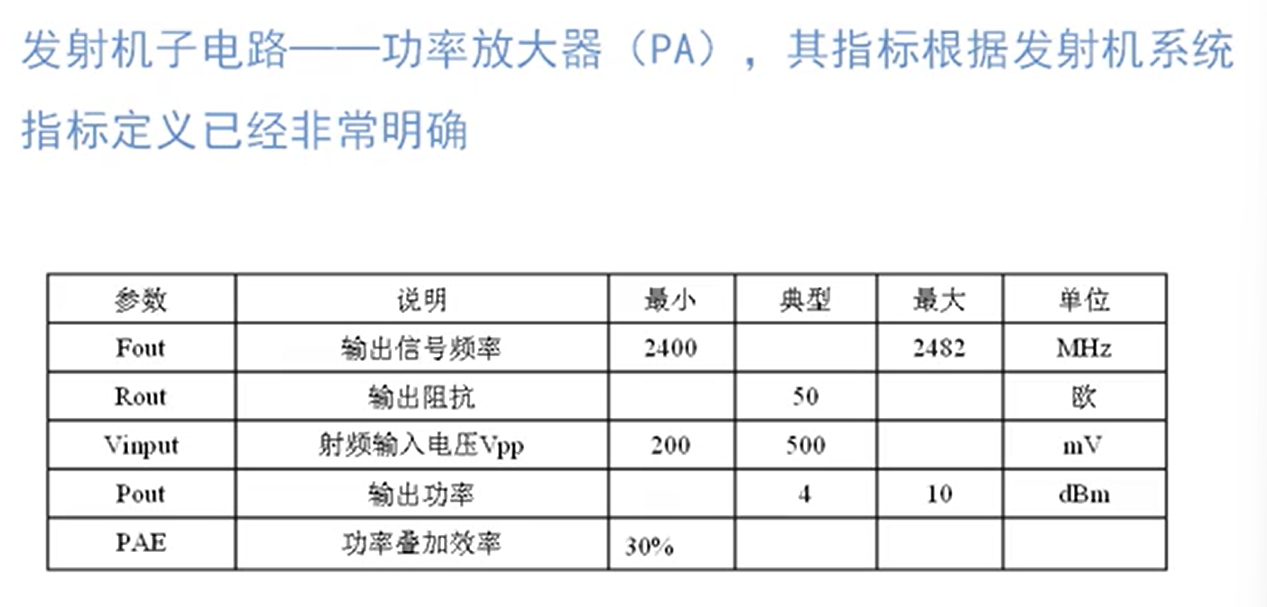

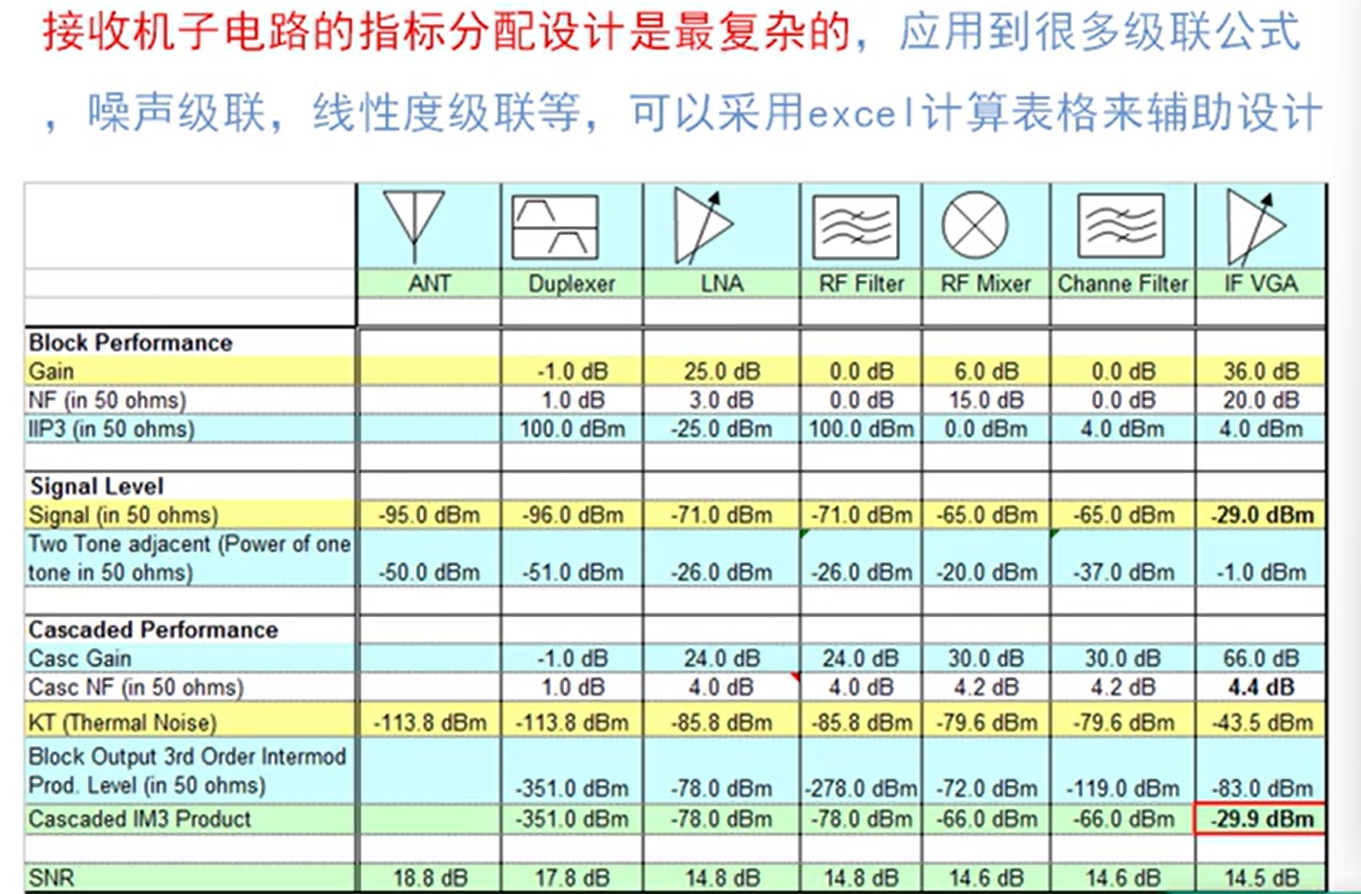

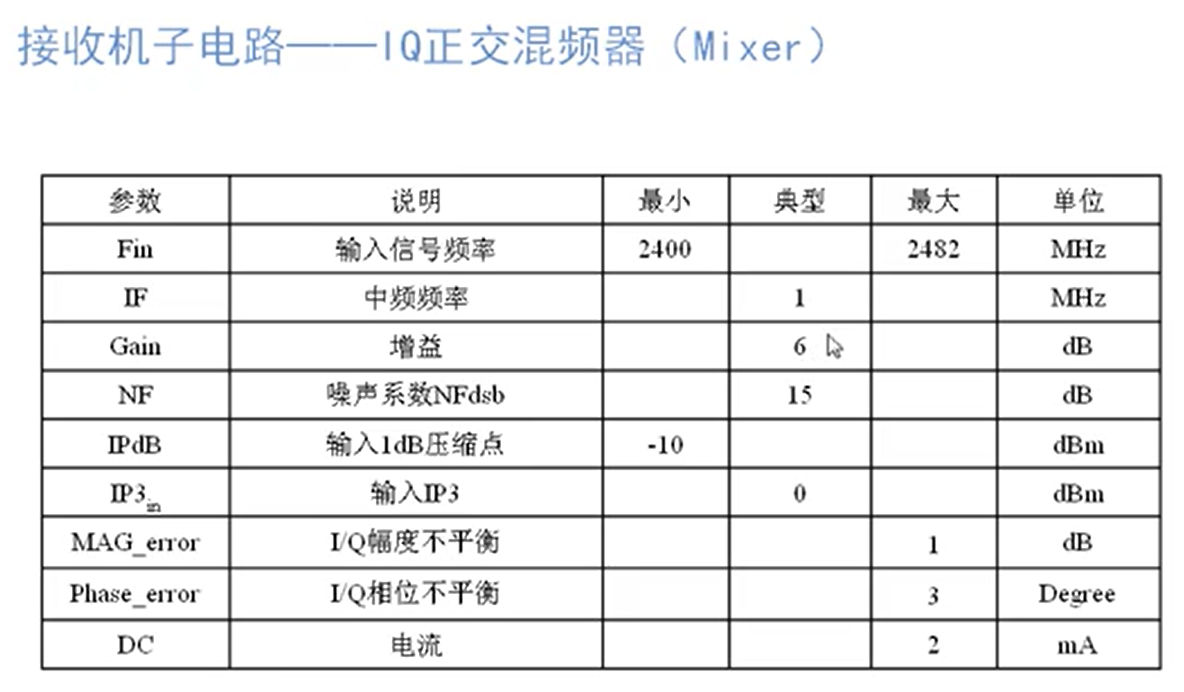

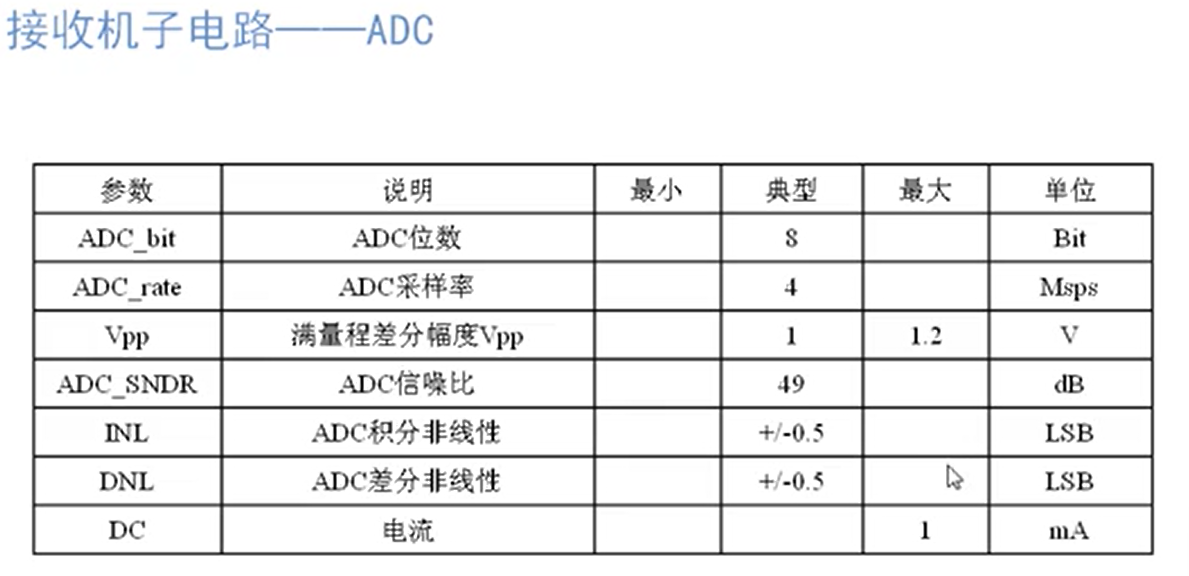

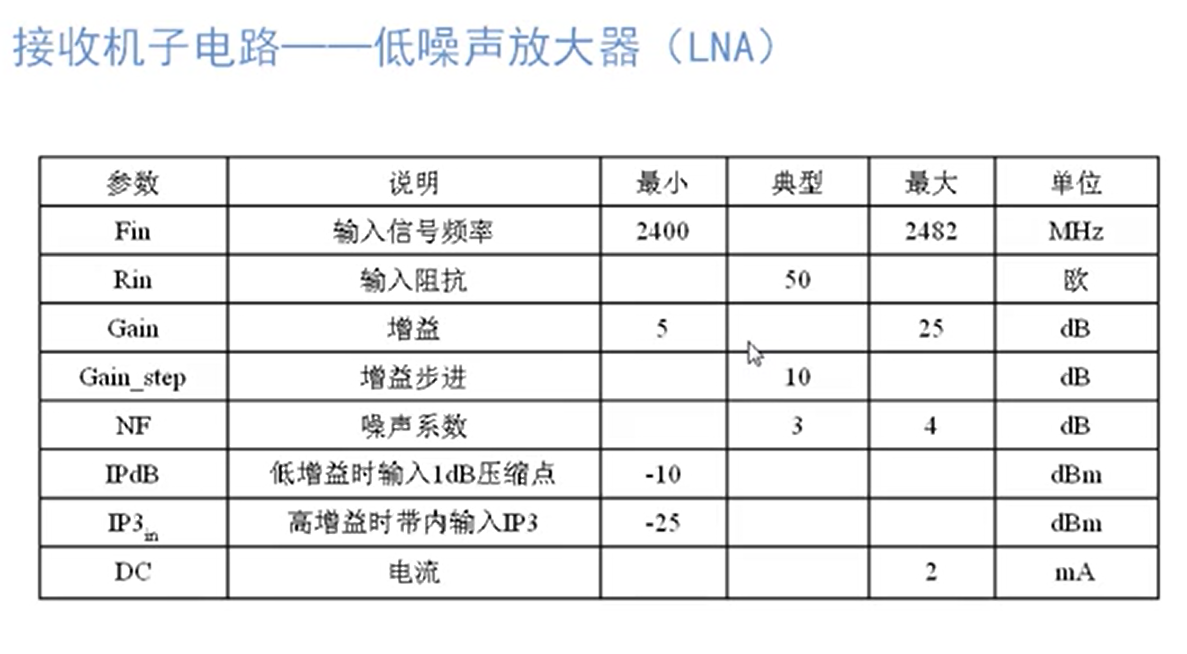

- Chapter Ⅰ 子模块指标要求

- Chapter Ⅱ 低噪声放大器

- Chapter Ⅲ I/Q混频器

- Chapter Ⅳ PA电路设计以及Load-pull仿真优化

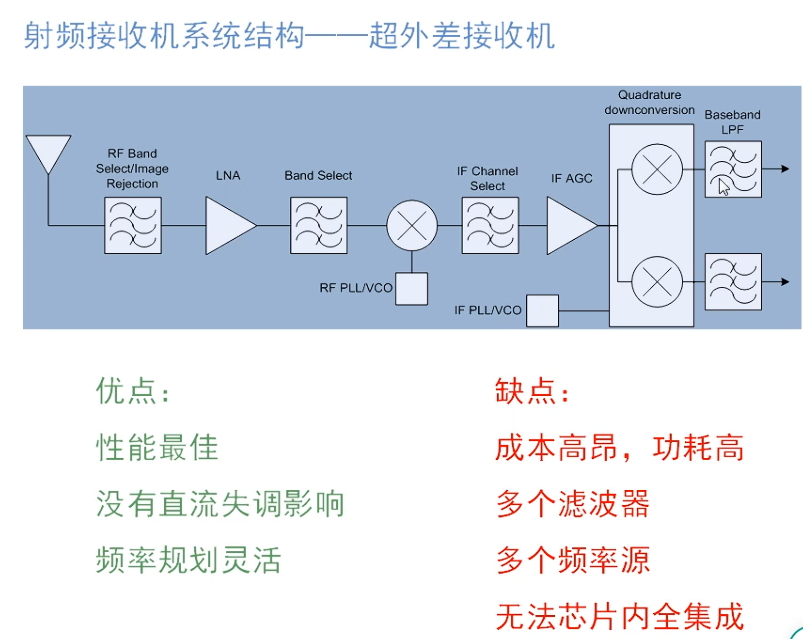

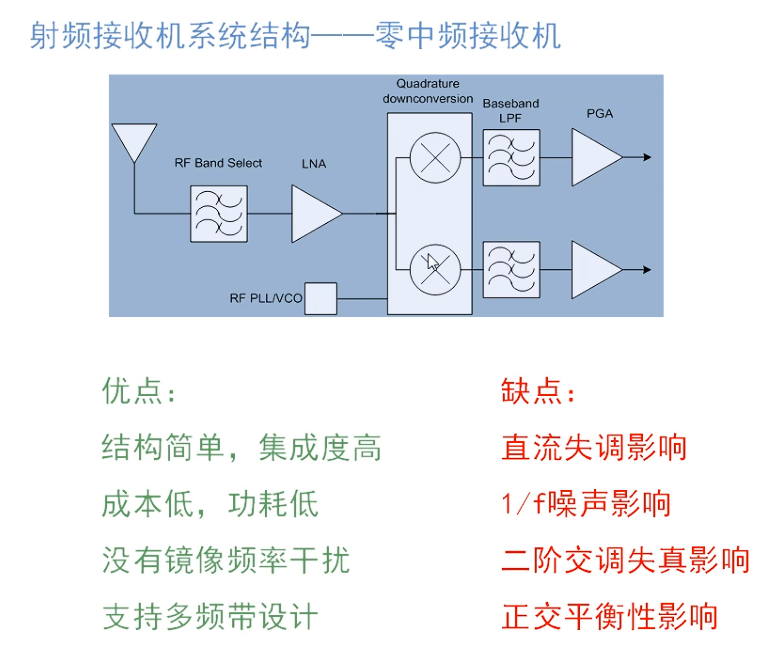

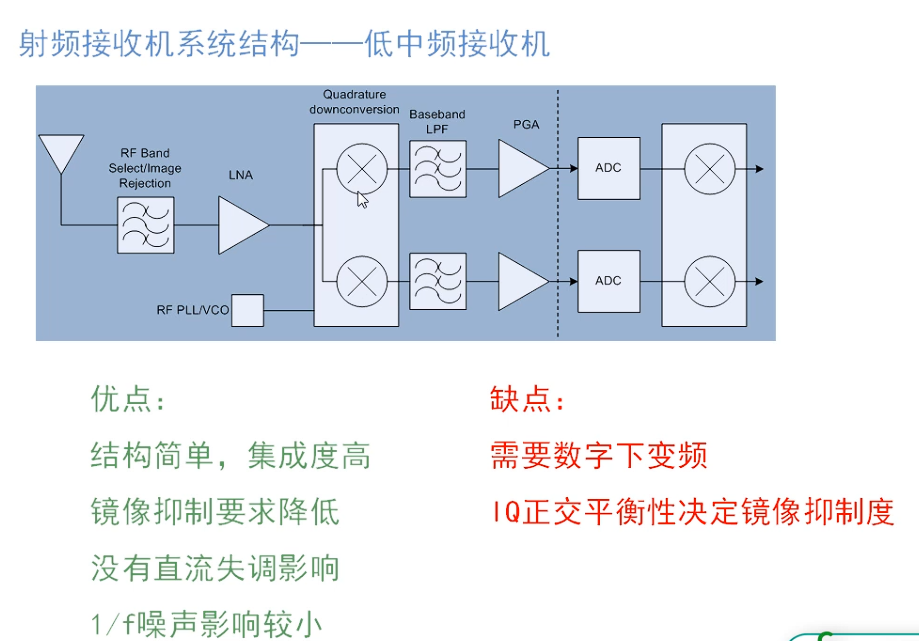

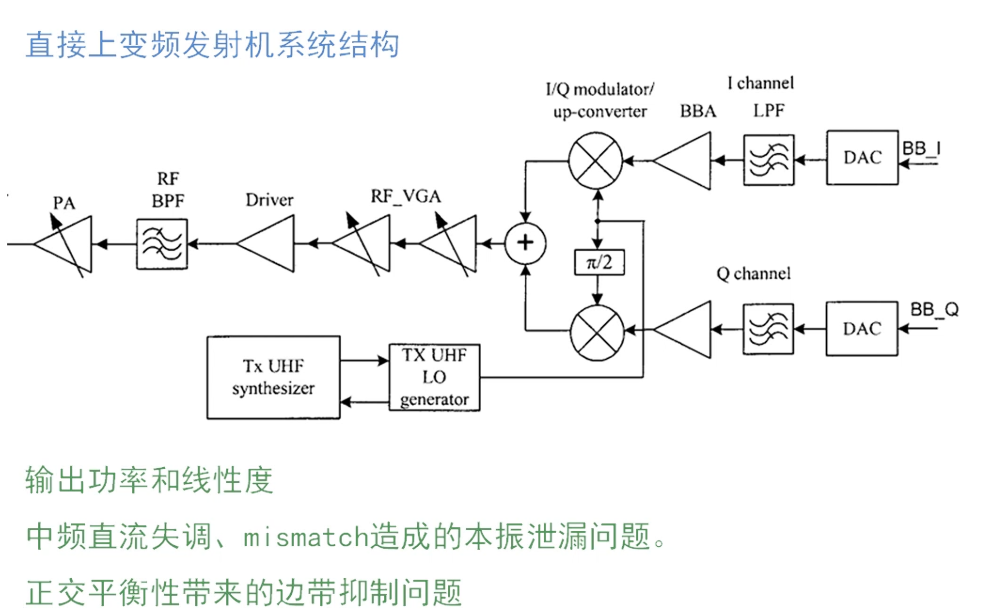

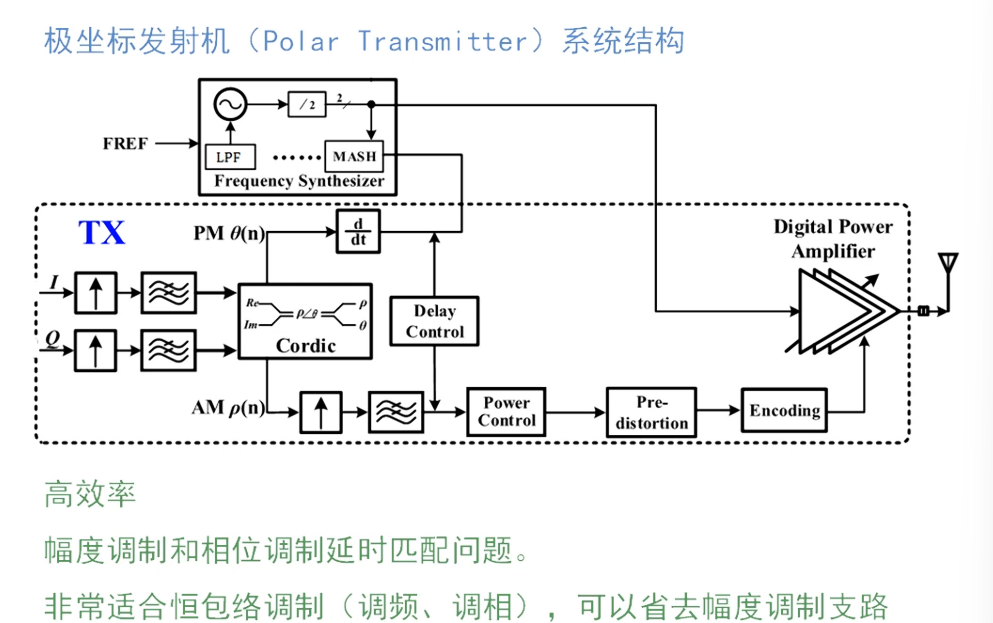

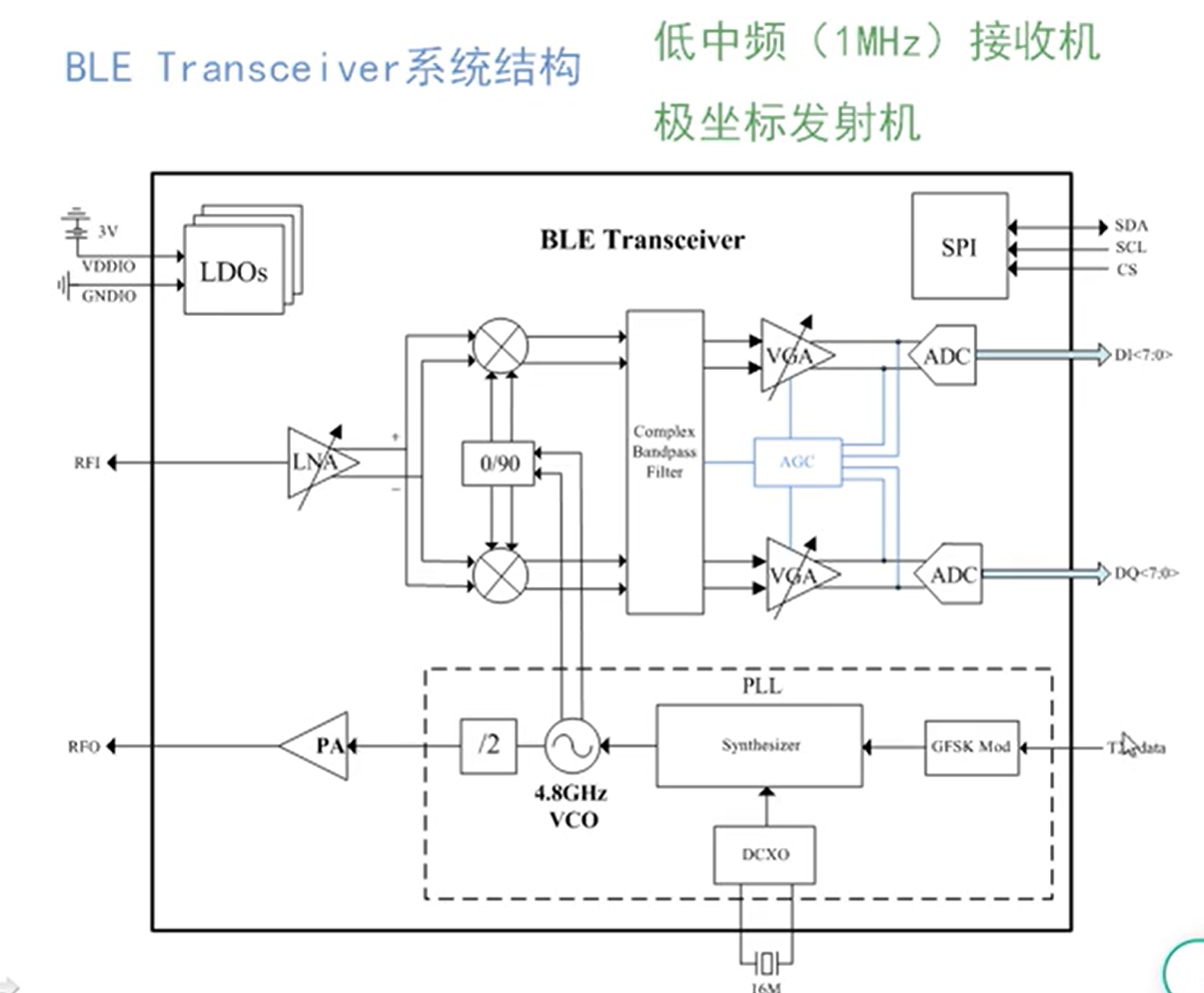

预学习阶段:接收机和发射机的结构概述

最适合恒包络调制,因为考虑到两路到达时延的因素

为什么要×2?BW只是基带的带宽所以要×2

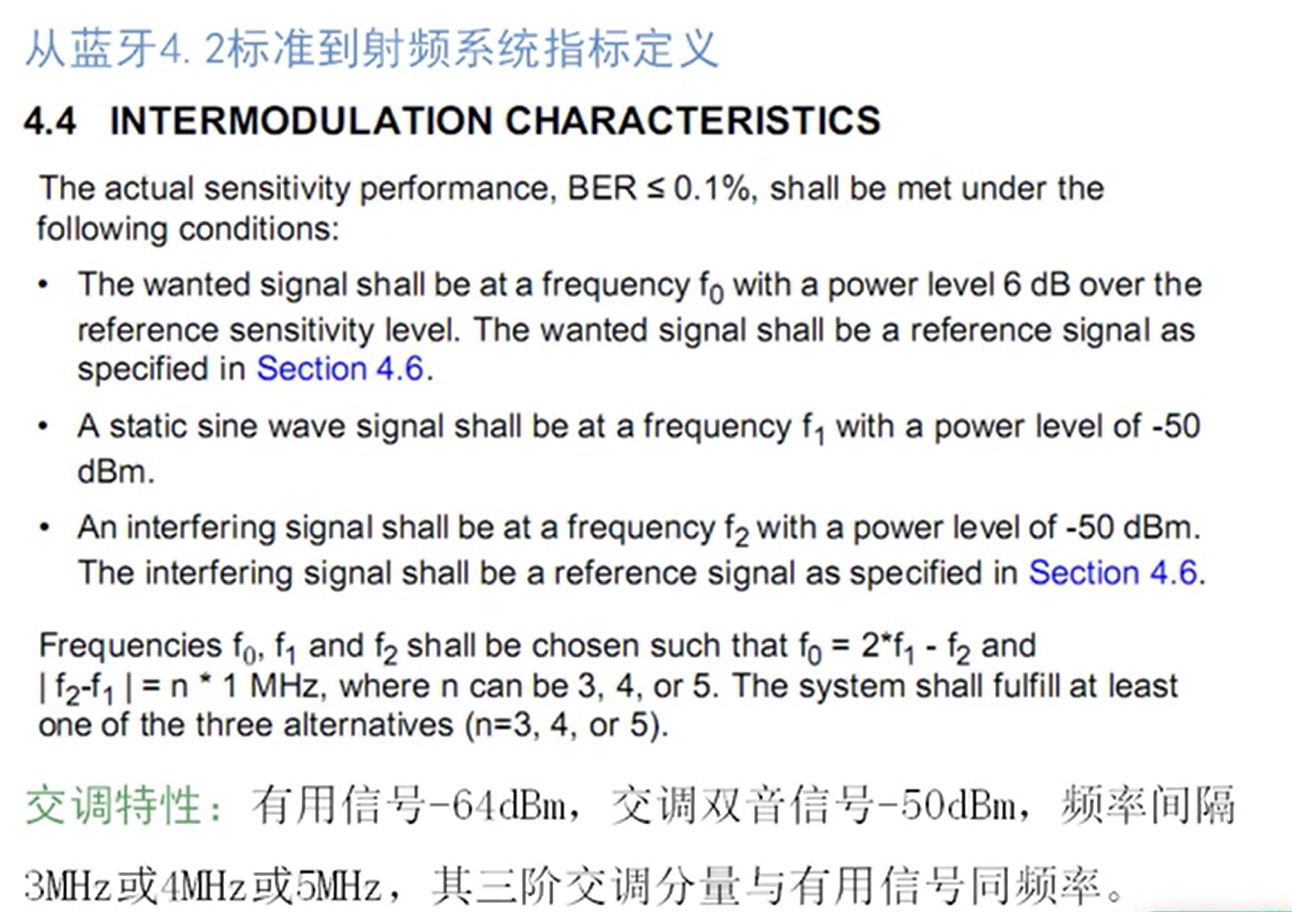

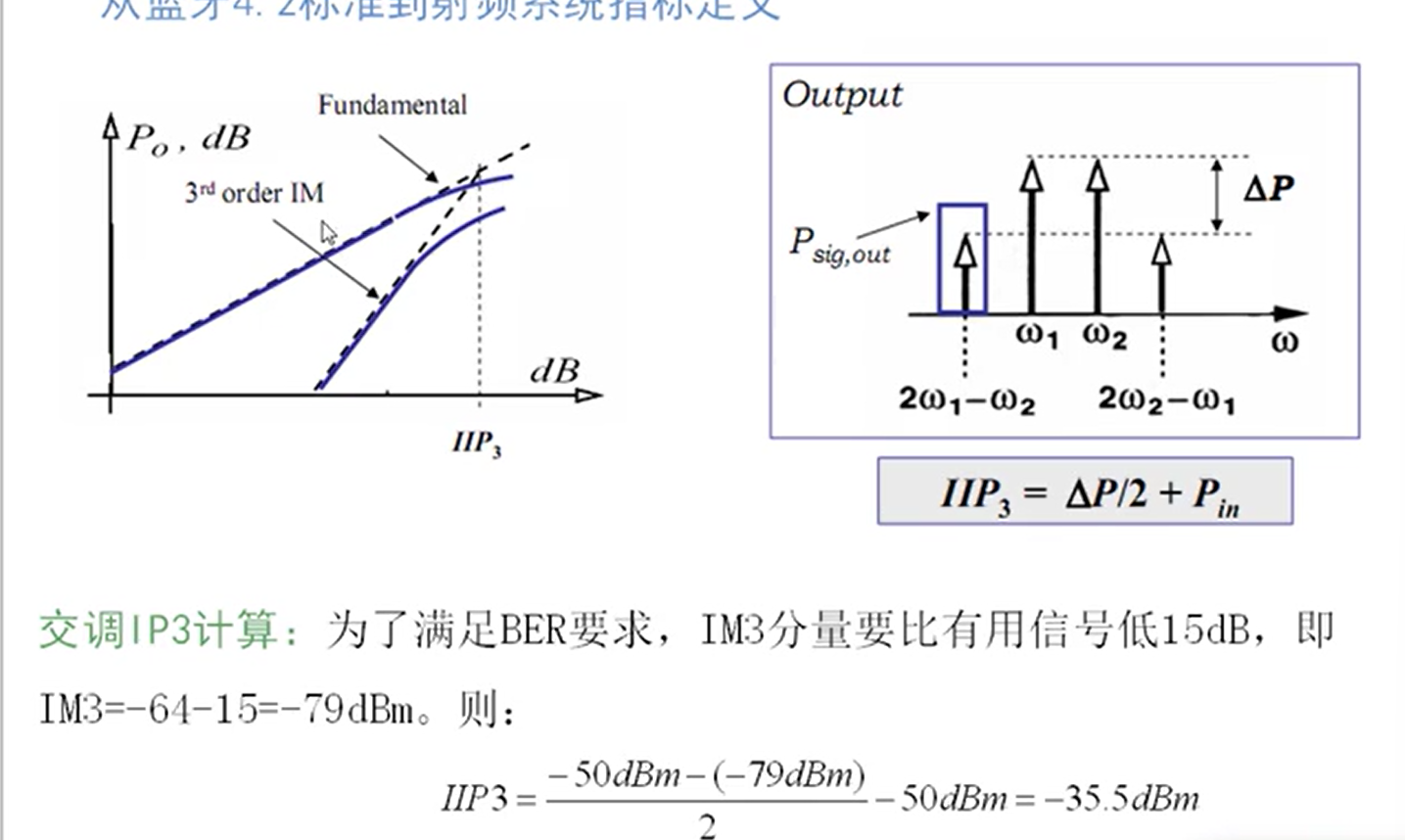

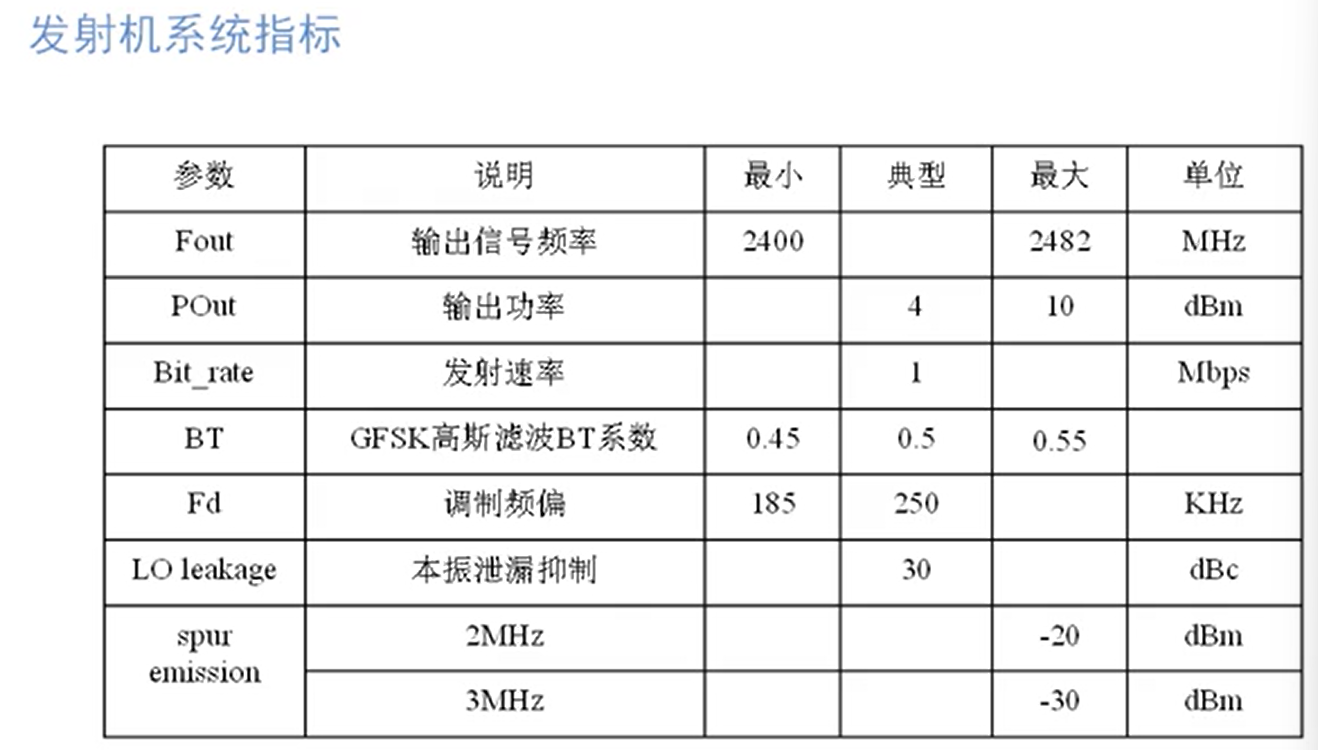

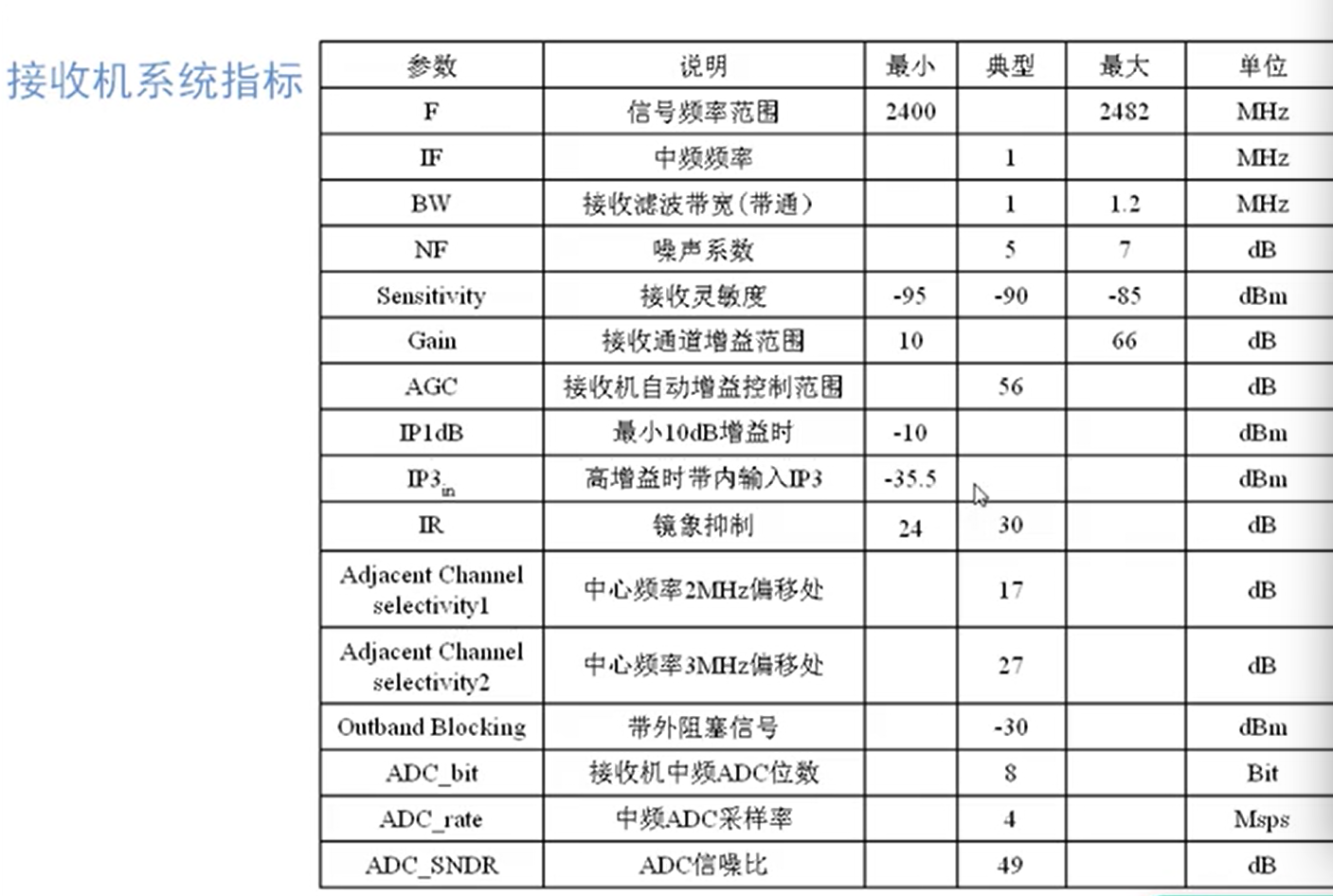

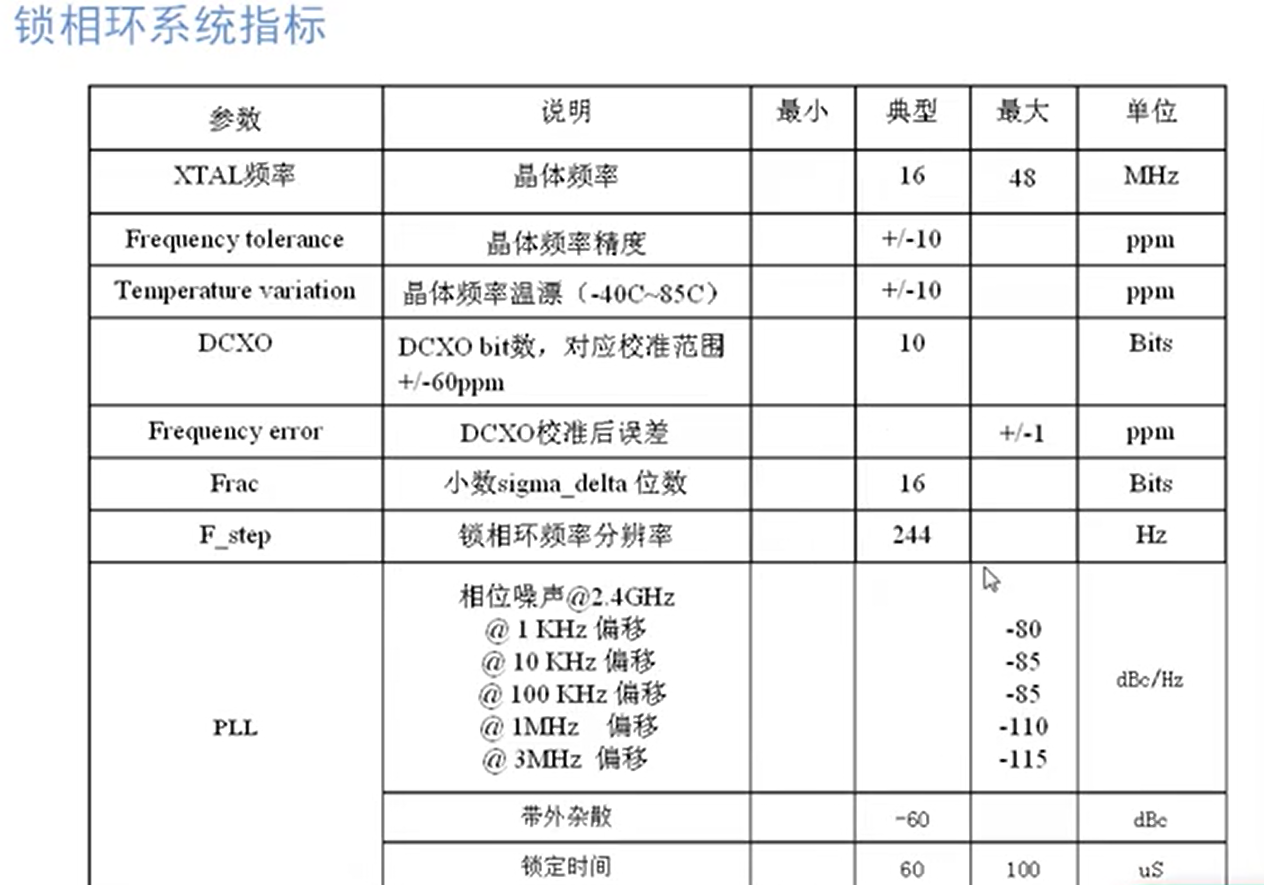

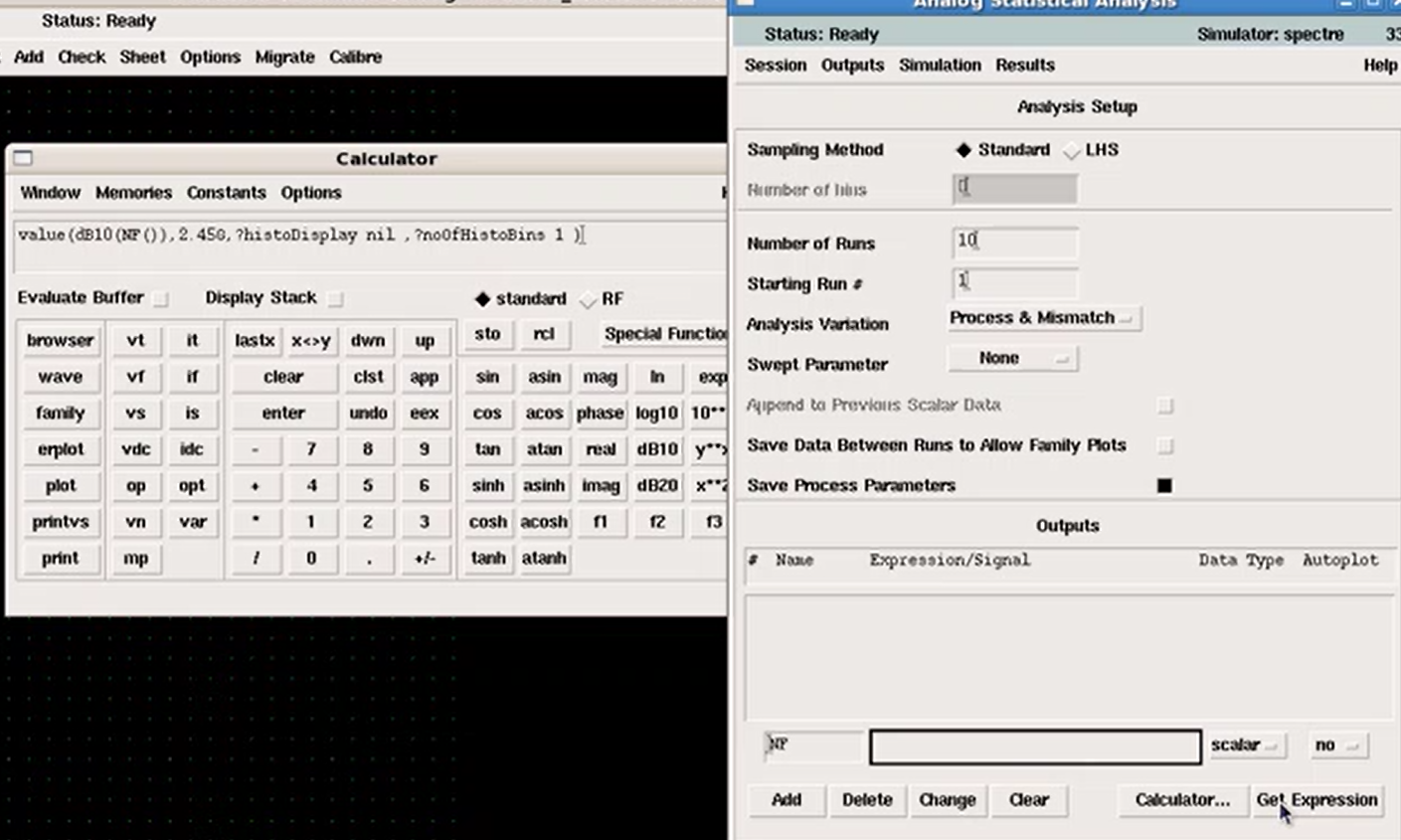

spec:

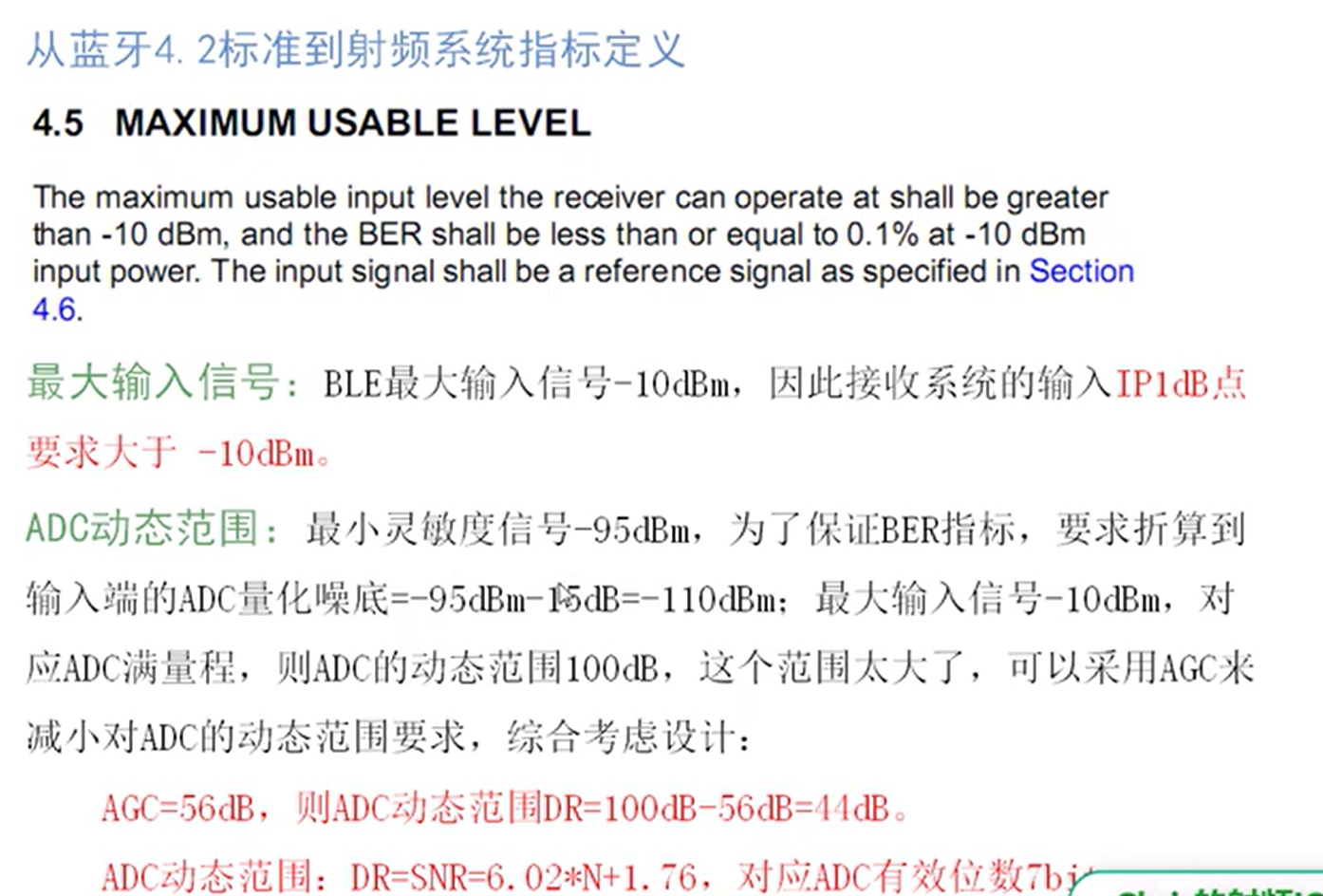

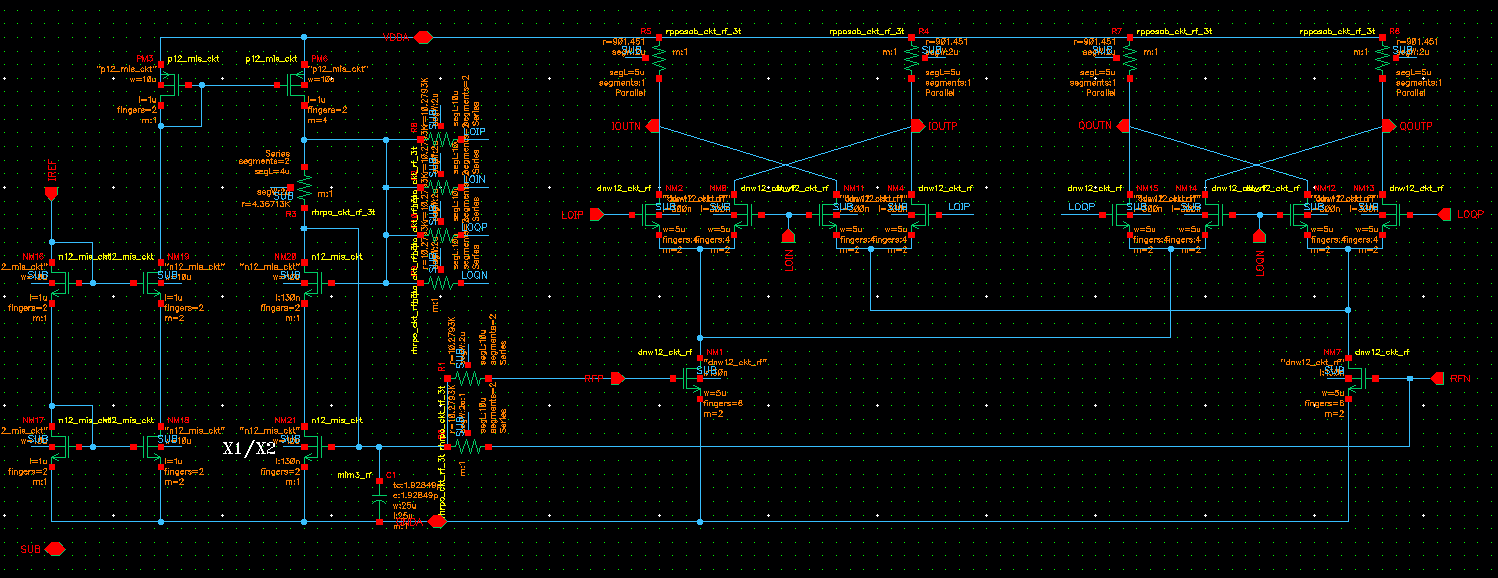

Chapter Ⅰ 子模块指标要求

基带信号要“预加重”,补偿低通滤波特性。将高频分量加重。

还可以采取两点调制方式。

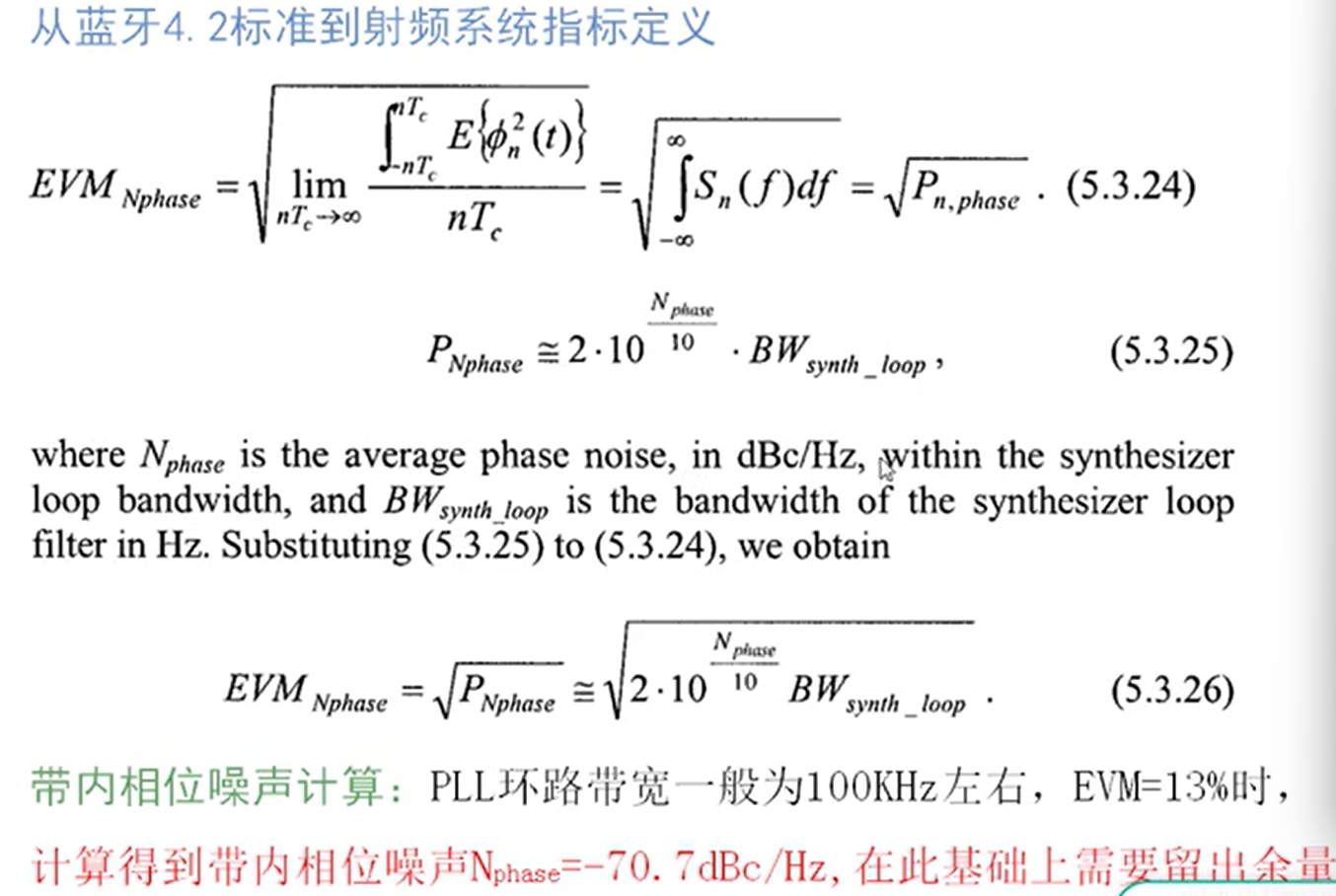

特别要注意电荷泵的电流输出,大的输出会使电路的噪声得到改善

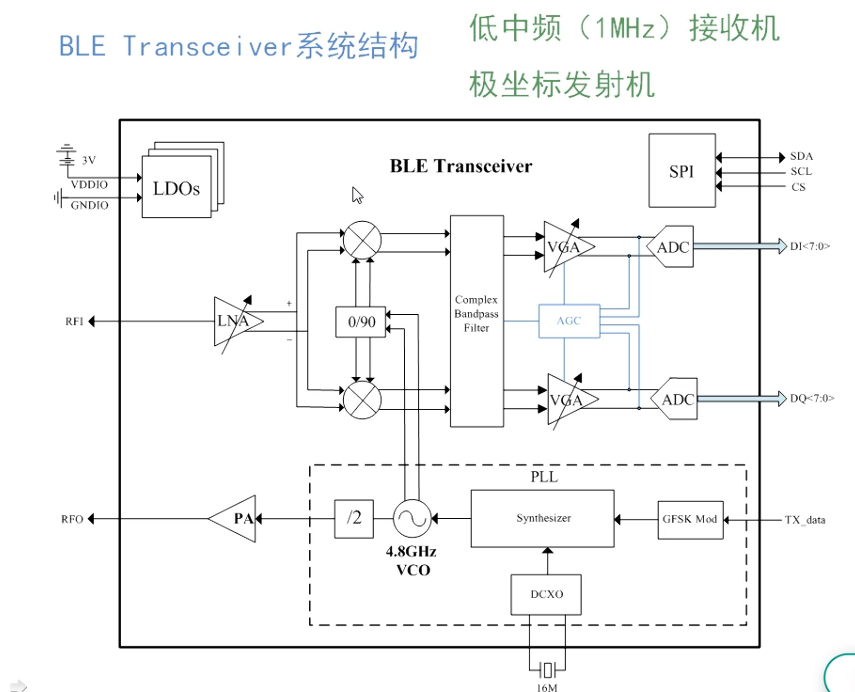

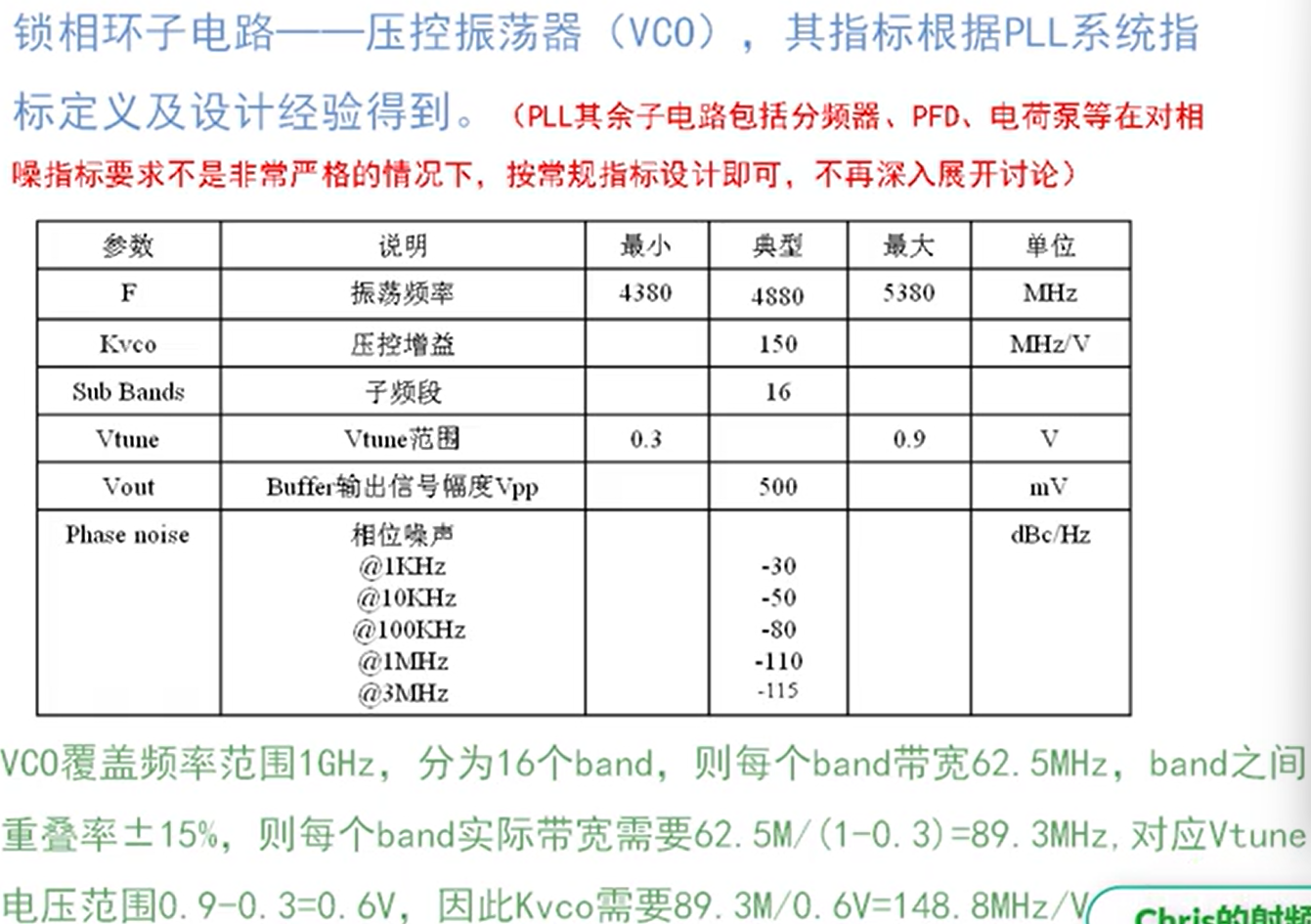

VCO工作在2倍本振,为了防止本振泄露和频率牵引等问题!还有考虑正交输出信号的相位差等原因

0.3V - 0.9V是为了防止电荷泵工作不正常

输出信号幅度不能太小防止后续的分频器不能正常工作

没正常分频相位噪声会改善6dB。所以远端的相位噪声会是1MHz - -104dB 3MHz -- -110dB

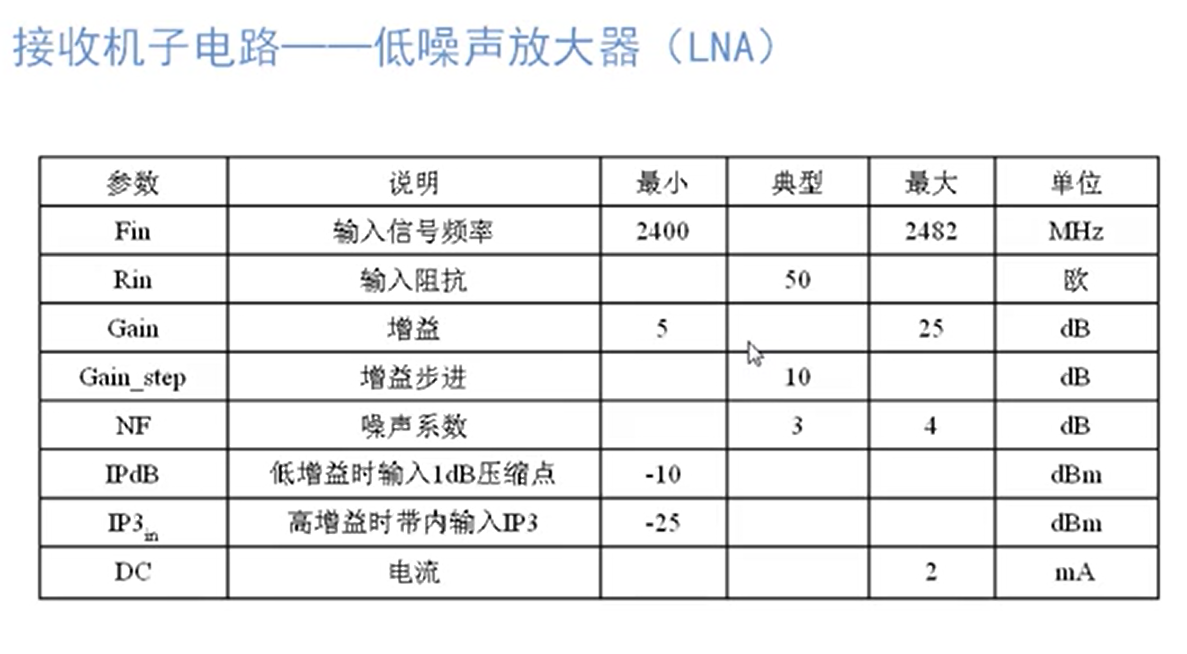

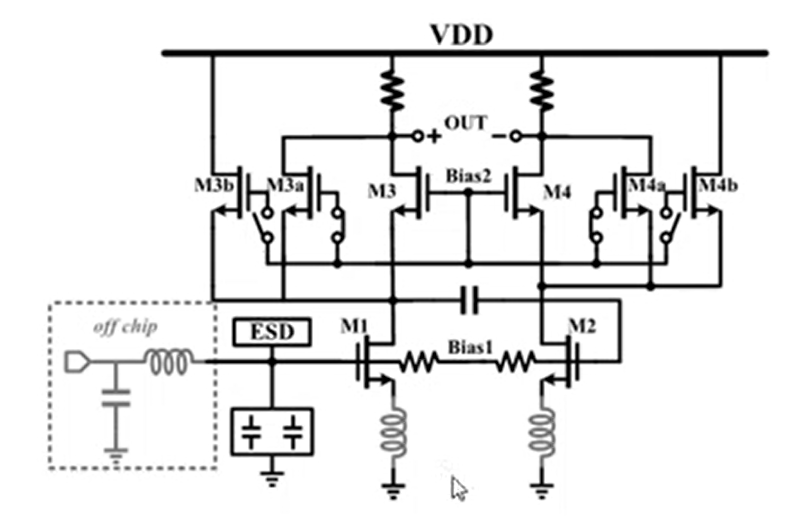

Chapter Ⅱ 低噪声放大器

单个晶体管的仿真分析

低噪放的结构:

所有的电感都在芯片外部!(外部匹配,外部引线电感)

使用单端转双端,避免了巴伦的使用

使用cascode结构,使用了米勒补偿!

注意M1漏断的电压增益近似为1,也即:

电压信号经过电容耦合到M2管子的栅端并被M2放大,因而生成了差分信号!

M3a,b 与 M4a,b用来控制增益(起到分流/旁路的作用)

CMOS射频晶体管噪声分析

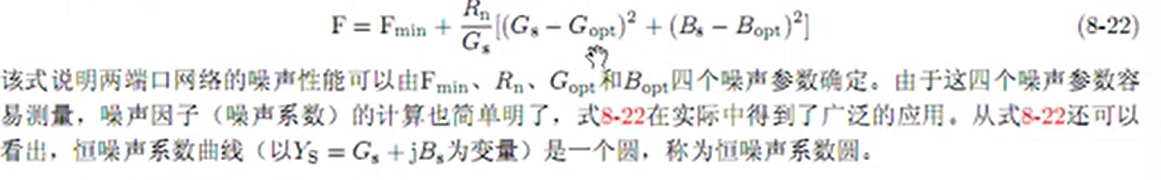

将噪声等效为噪声电压与噪声电流,分析得:

主要噪声来源:漏端沟道电流热噪声,栅噪声。

参数设计过程

首先要确定单个晶体管的特性。

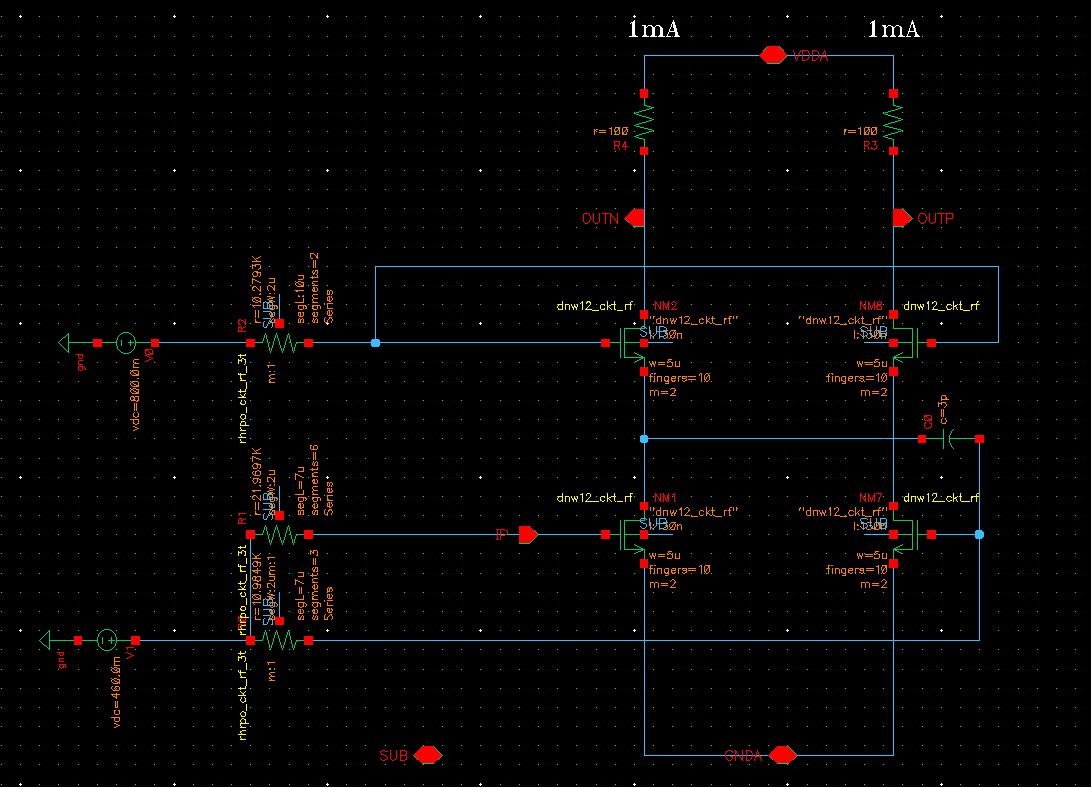

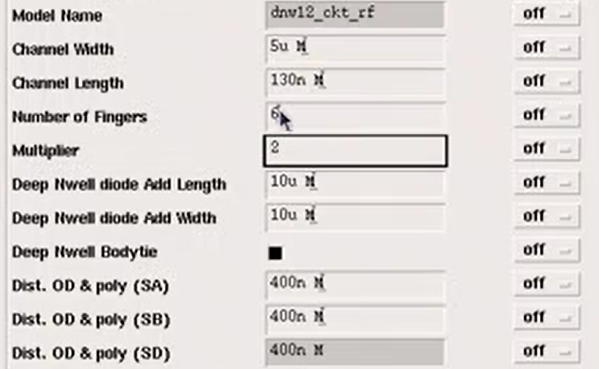

为什么使用DNWELL的晶体管?因为整个电路会放在单独的DNWELL上防止干扰。

下方gnda设置为引线电感模型(1uH,50欧姆)

栅极的直流使用直流偏置时使用1uH的电感防止交流信号进入电源,同时加隔直电容防止漏电。

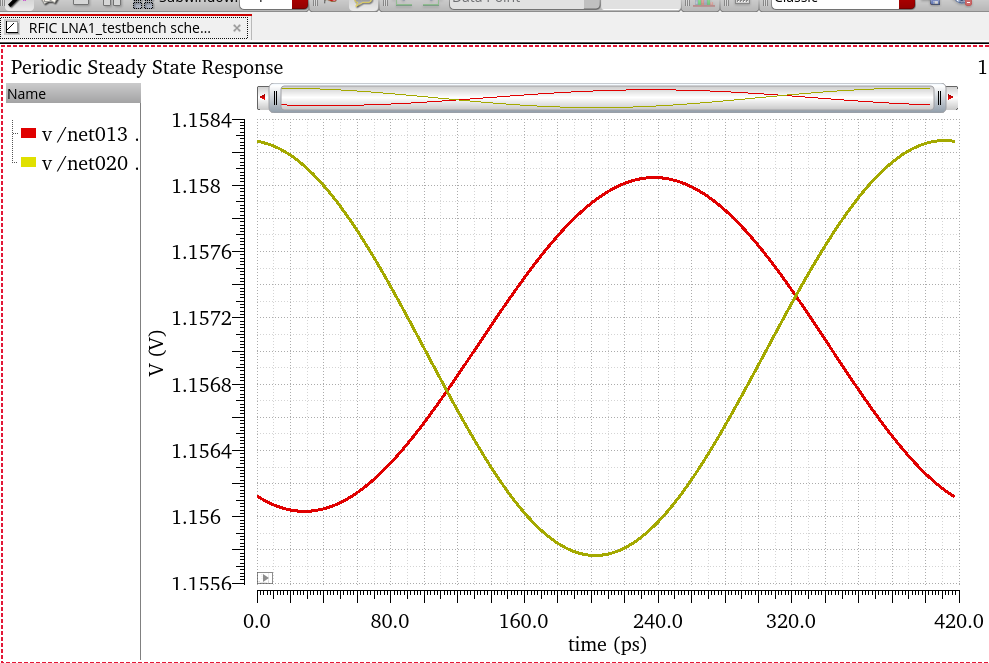

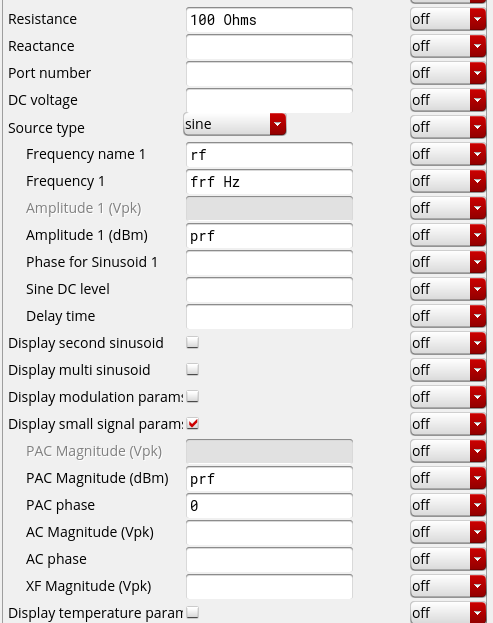

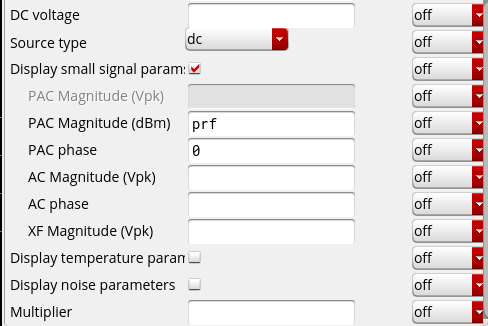

port的类型选择sin输入,输入功率和频率。

小信号的参数设定AC的幅度1V与相位0°

晶体管的漏端加入射频扼流圈1uH接到VDD;输出port设置为负载端,阻抗为1k欧姆(大概的高阻抗负载)

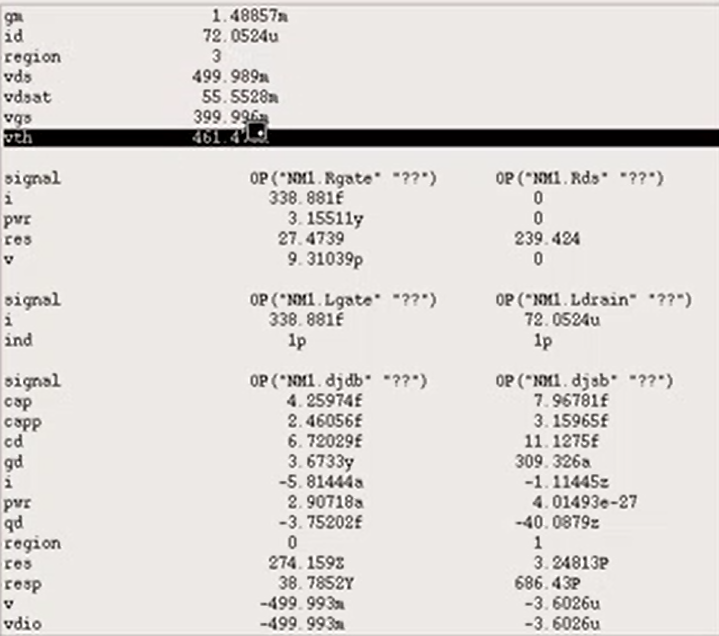

首先分析dc仿真

扫参数:输入信号功率,叉指数,工作频率,偏置电压幅度,VDD

print出管子的参数:

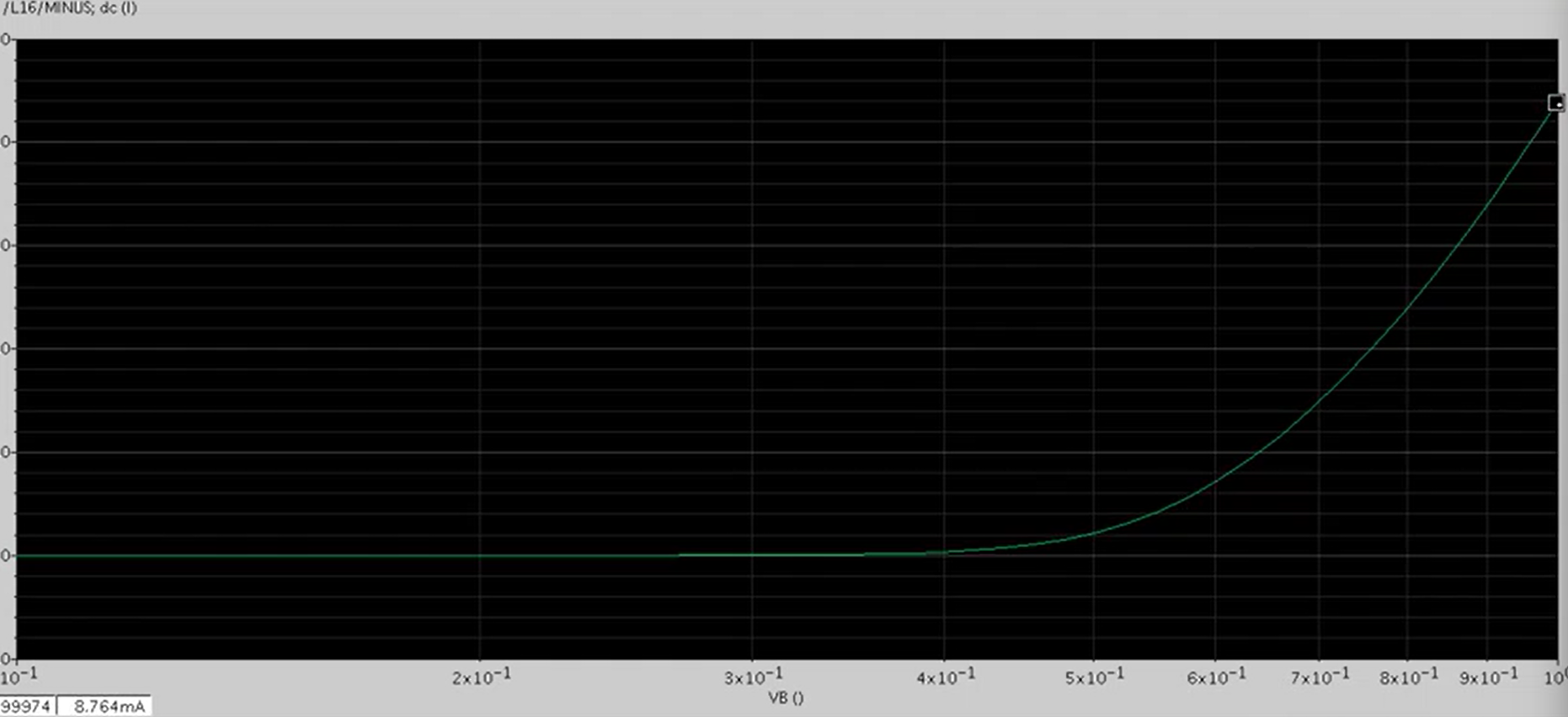

再作出电流消耗:

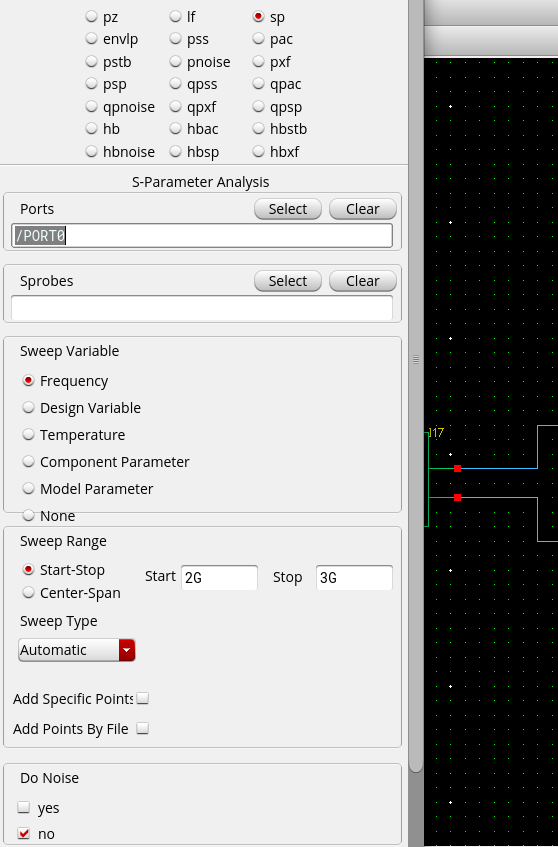

使用s参数的仿真

在固定的VDD中进行频率的扫描/变量的扫描

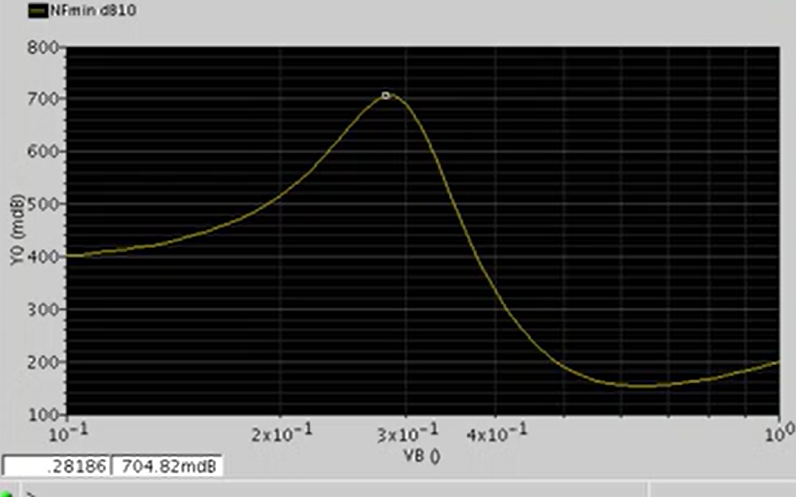

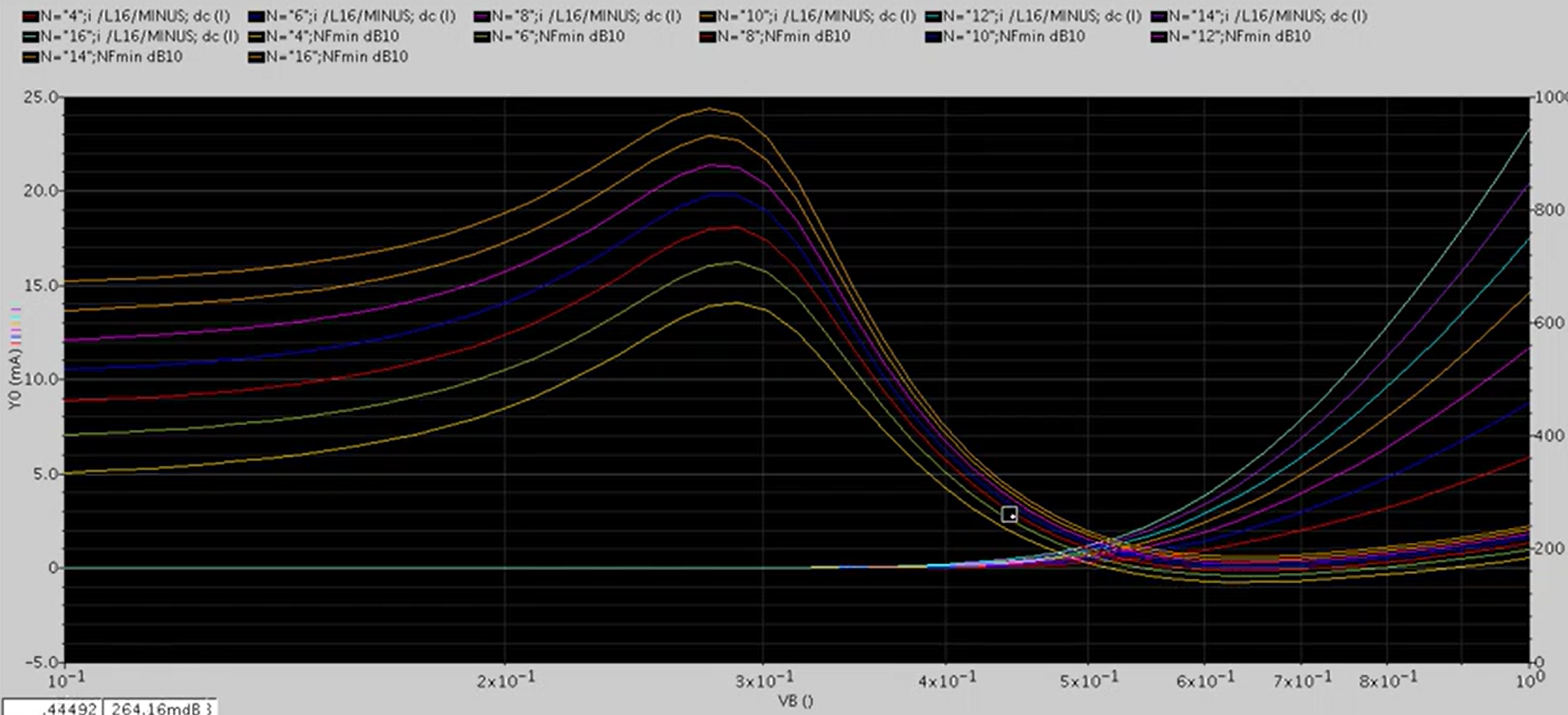

首先扫描2.4GHz下的偏置电压:

要选噪声分析!!!

因为此时输入输出不匹配,看S参数无多大的意义,应重点关注最小噪声系数

再扫描最大电压增益

考虑到晶体管的最大电流,综合最小噪声系数,功耗,最大可以增益选择

采取3pF的电容进行交流耦合形成差分信号

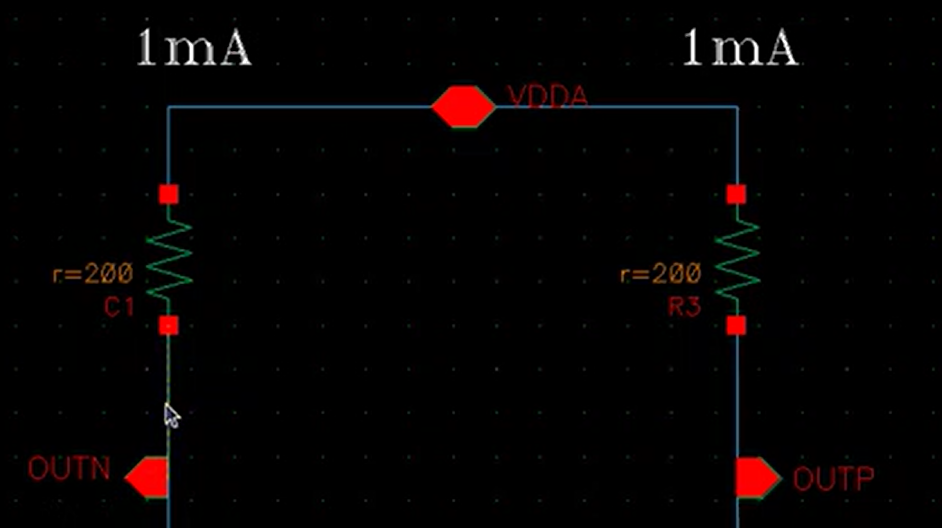

采取阻值为200欧姆的负载电阻,以后还需要根据线性度和增益进行折中考虑。

此处的阻值选取不能使管子进入线性区,并且要允许输出的电压有足够的摆幅,

根据管子的Vdsat关系确定共栅极的偏置电压约为0.8V(尤其要注意PMOS的衬偏效应))

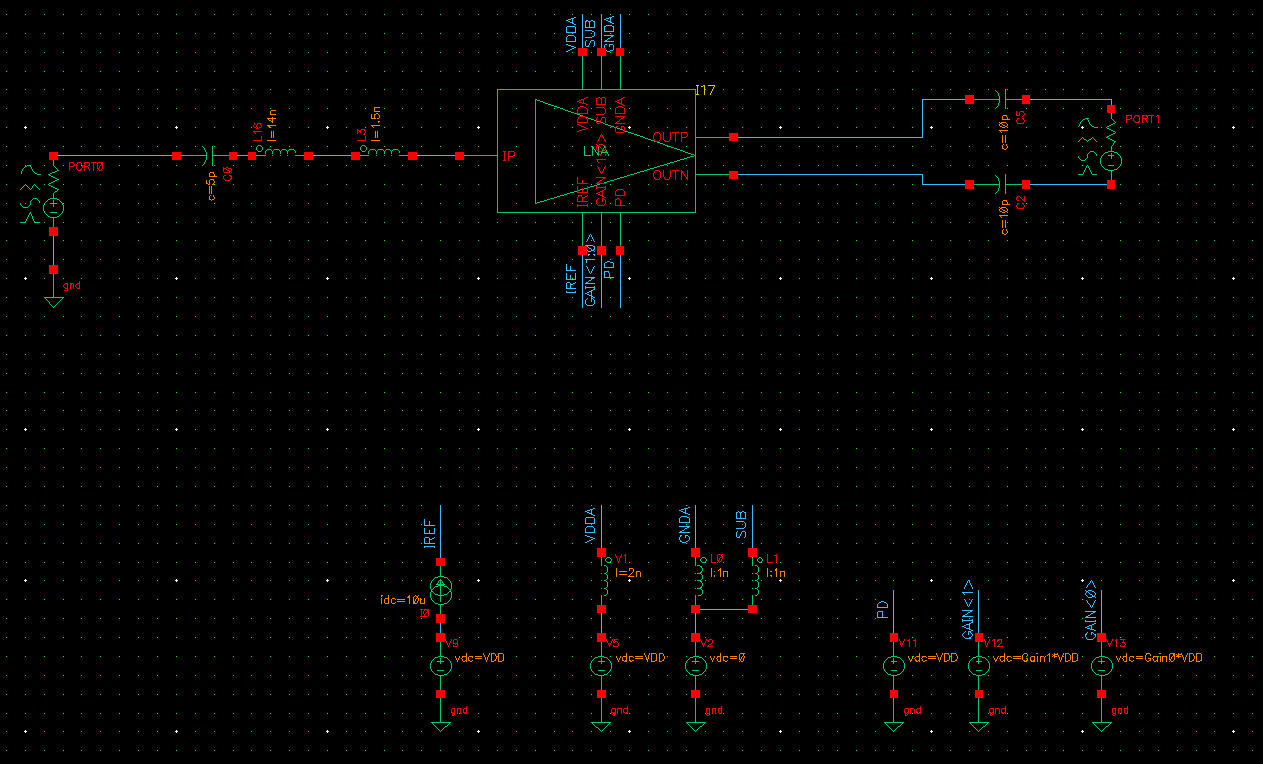

核心电路以及sp,ac仿真

Testbench的搭建

首先计算共栅极晶体管的栅极直流偏置:

首先负载电阻上面的电压降为0.2V

过驱动电压指的是

而且共栅管由于衬偏效应,其

取过驱动电压为100mV,则共栅管的栅极偏置要设定为:

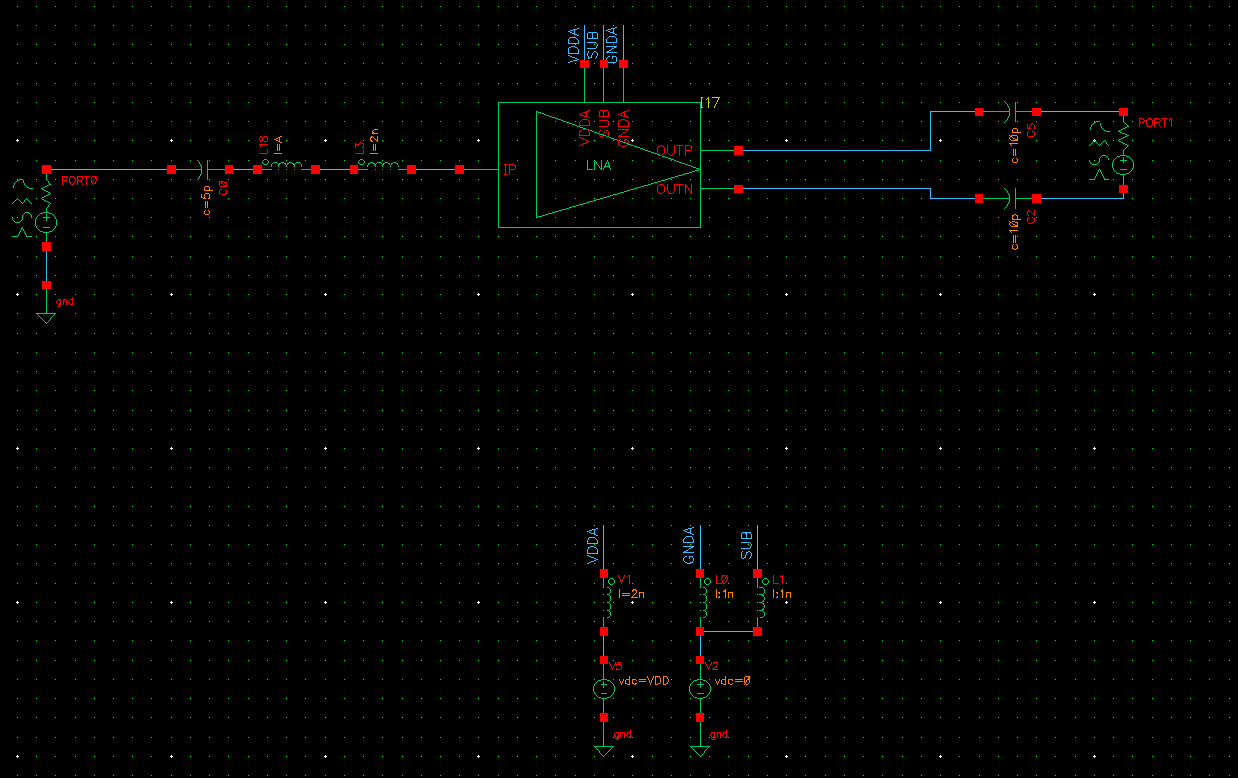

在这里,输入端还要模拟外部因为QFN封装引入的引线电感,并且使用LC串联部件将其匹配到输入端口上面。引入的寄生电感的电抗值设置为2nH,电阻设置为100欧姆,下一级混频器的输入阻抗设置为典型的1k欧姆。

首先检查直流仿真:看到子电路当中的电流大小为2.5mA,造成了较大的功耗,这个时候就要改变晶体管的finger数目调整电流大小。

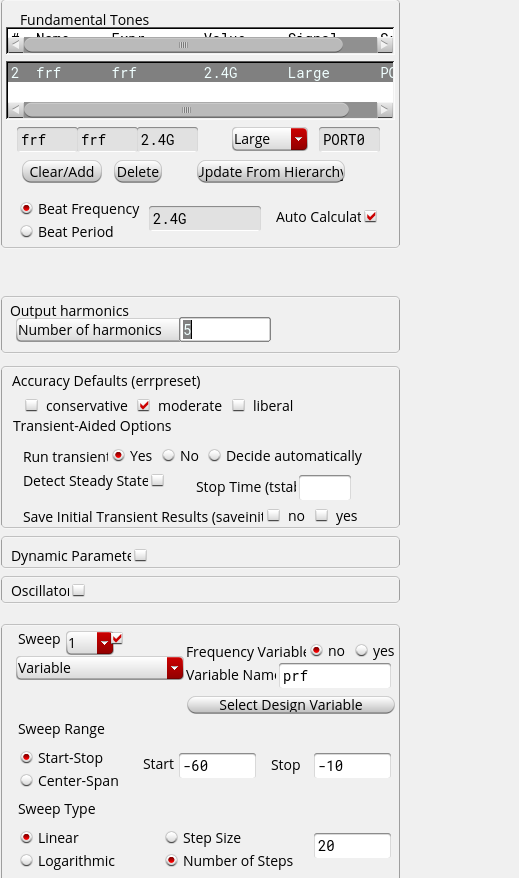

然后进行sp仿真,注意选择噪声。

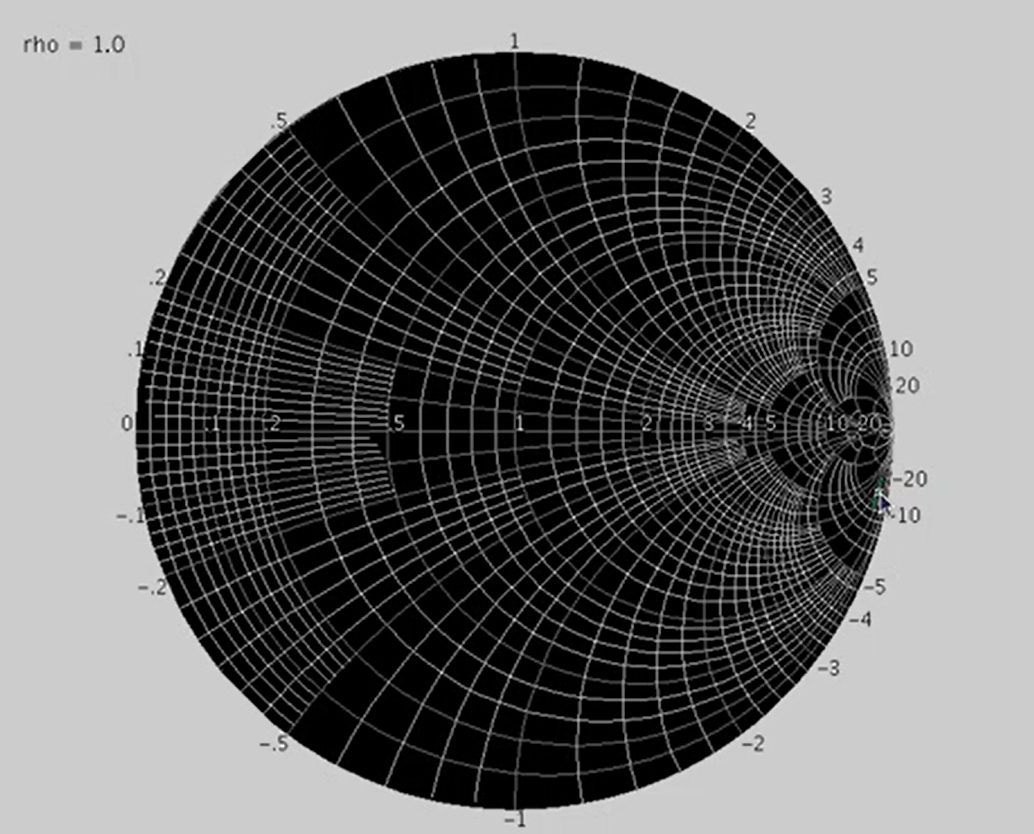

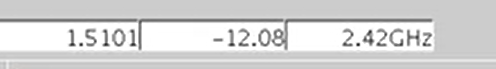

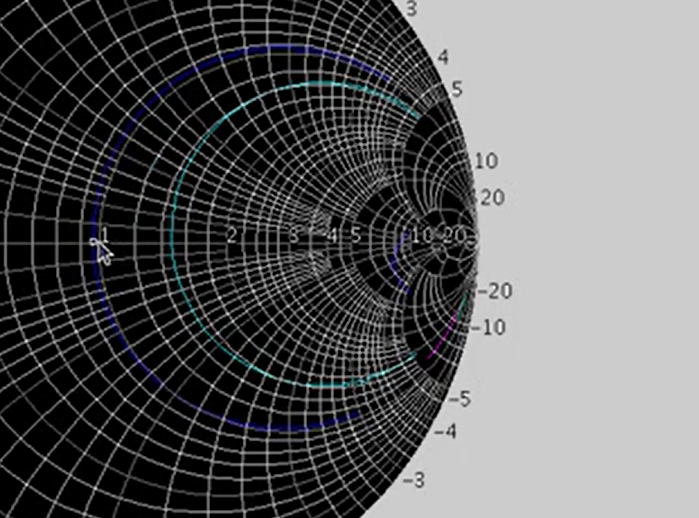

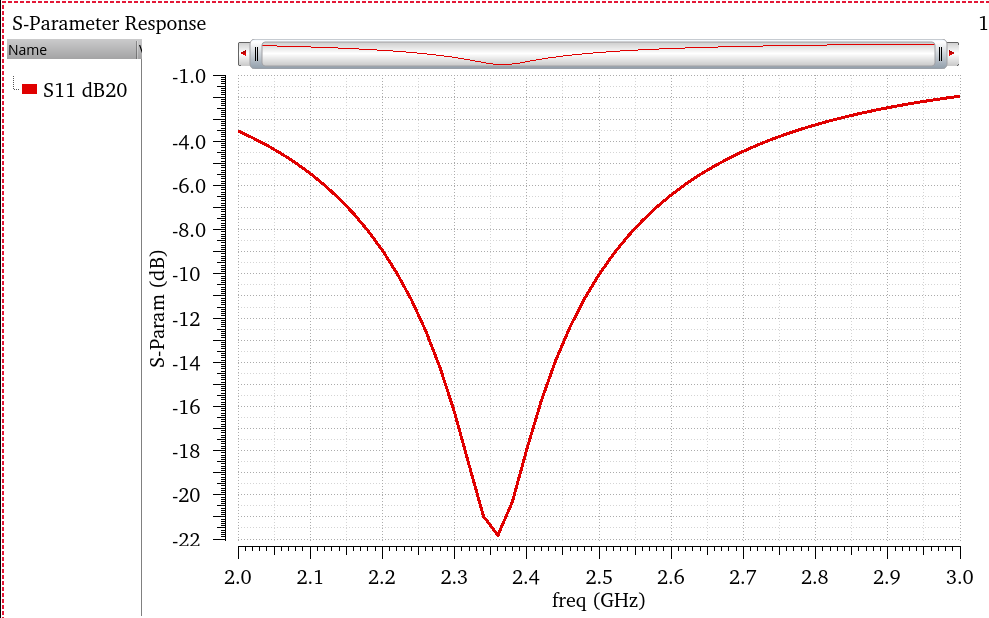

首先看输入阻抗的匹配,查看史密斯圆图(Z_Smith)

发现S11大多数位于右下方,这样的带宽会比较窄,这样比较难以匹配(归一化后的结果见下)

实部在75欧姆左右大致符合,主要在于将虚部抵消掉。将匹配电感调整至38nH,得到:

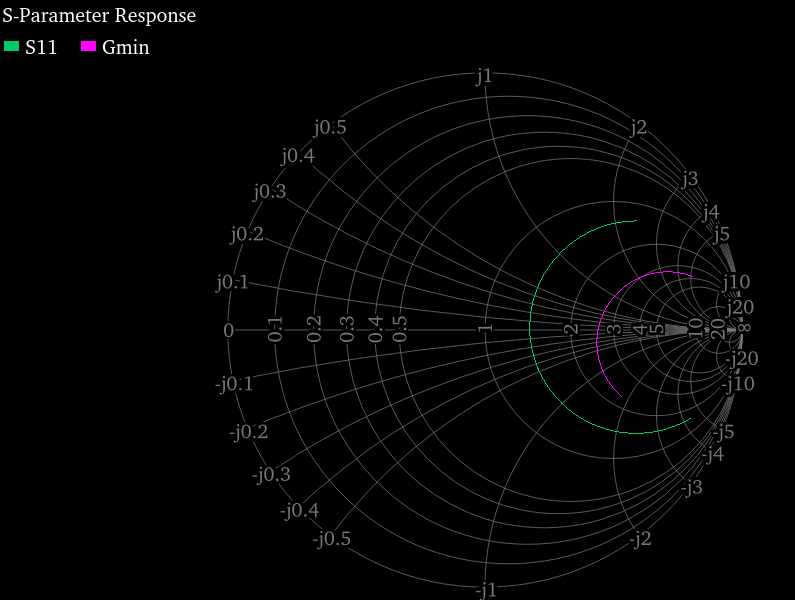

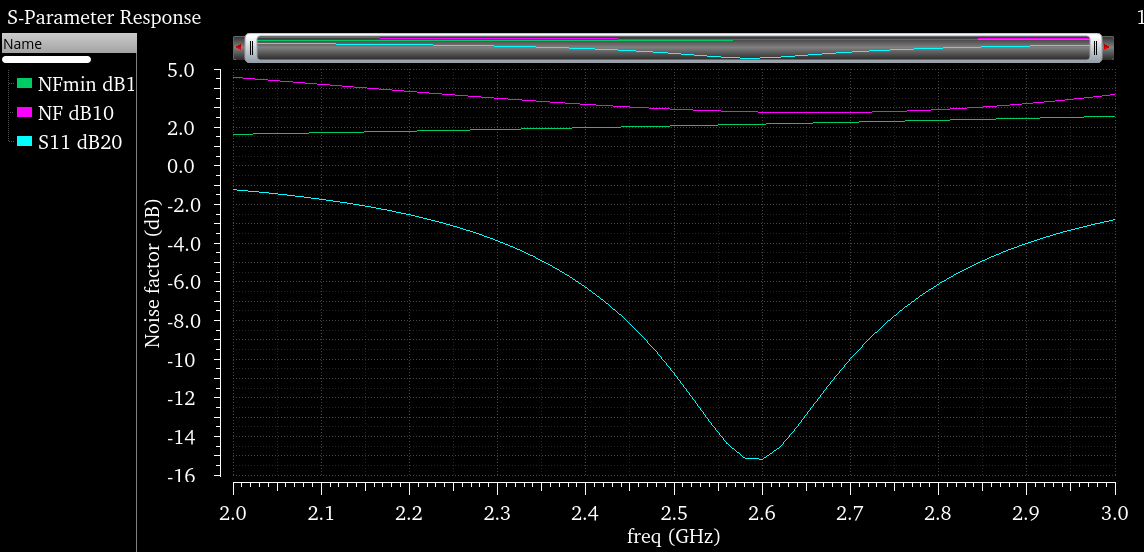

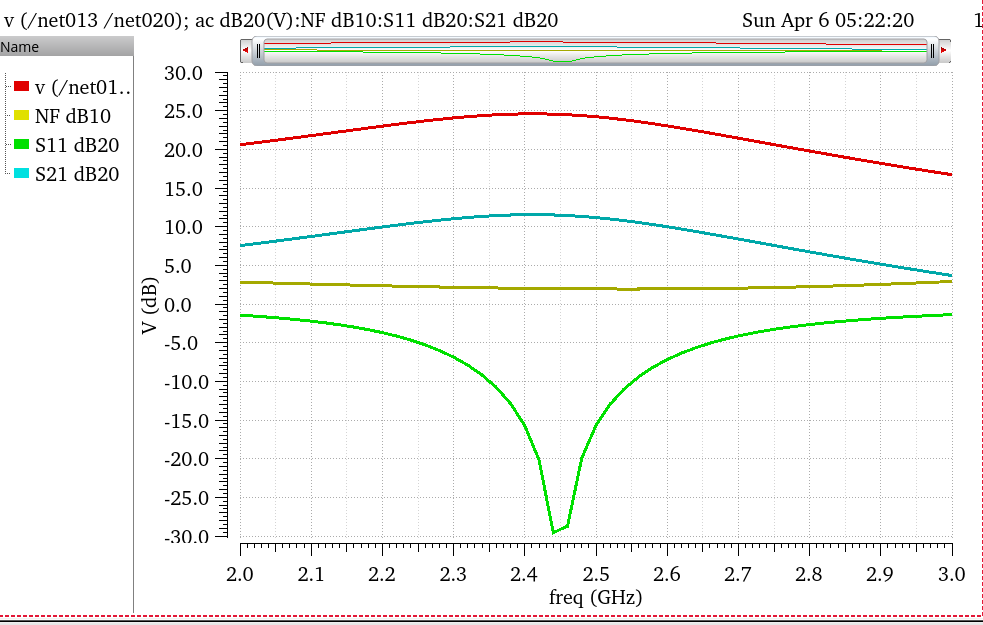

通过调整匹配网络当中的匹配电感,查看最小噪声系数与S11

此时发现二者有较为严重的偏离,这样就会使噪声系数较差

当S11和Gmin参数曲线共轭对称时效果最好

此时主要是实部的偏离较大,虚部也有很大的影响。

此时调整晶体管的finger值进一步进行调整,但是dc需要重新调整栅极偏压!

上图查看S11 S21 最小噪声系数NFmin,噪声系数NF

要注意源阻抗和输入阻抗的共轭匹配条件,

要注意晶体管在亚阈值区会导致噪声大幅度恶化!

最小噪声系数对于偏置电压的变化很敏感!(工作电流)

进行ac仿真:注意输出使用差分计算

调整负载电阻观察增益的变化,以满足要求。

还要分析相位平衡性与幅度平衡性

调整平衡性可以调整耦合电容/调整一侧的负载电阻

但是可能会带来噪声和增益的恶化!

噪声,线性度以及稳定性仿真优化

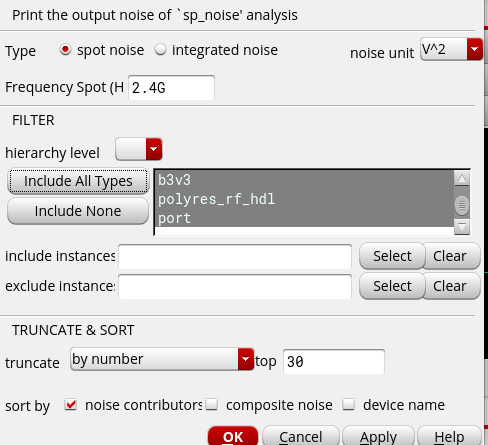

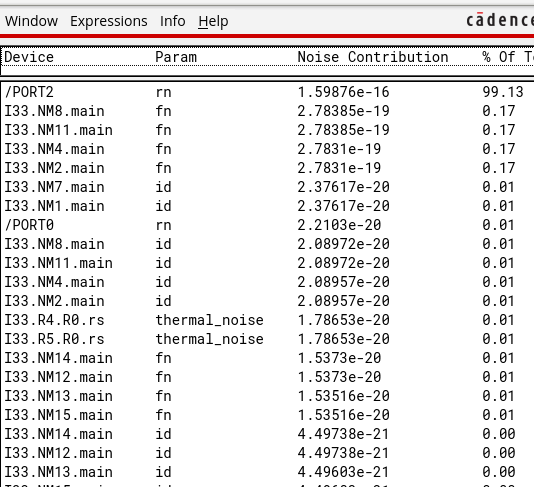

噪声分析汇总:选择result - print - noise summary,选择前30个噪声来源

可见输入port的热噪声占比最大,其次是晶体管的沟道噪声,以及负载电阻,偏置电阻的噪声

根据来源的占比可以修改器件参数从而改变噪声的贡献,比如对于偏置电阻的改变。

使用pss仿真进行线性度的仿真

pss:大信号进行稳态仿真,在其上叠加小信号的运算。

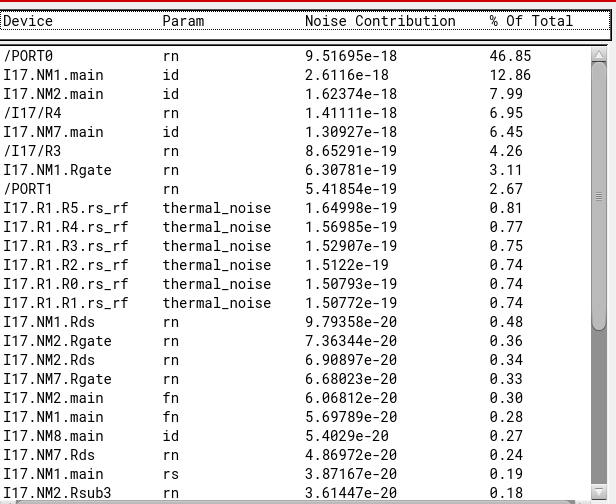

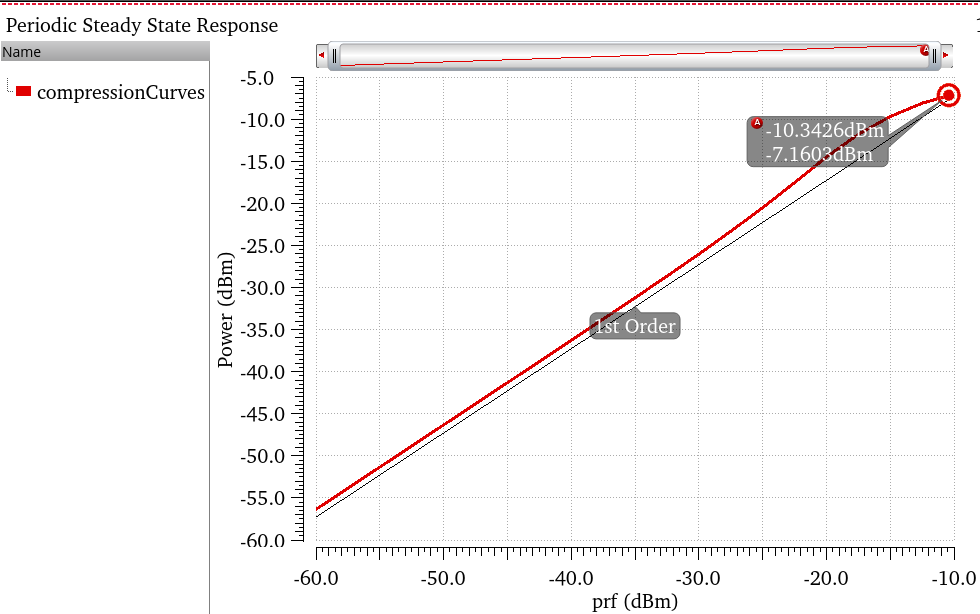

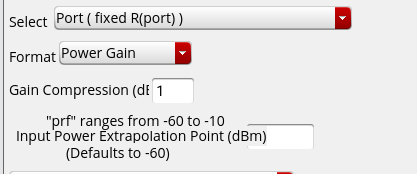

输入单音信号,输出的谐波数填写想要查看的谐波数,稳定时间是要先进行瞬态仿真;要扫描输入信号的功率,以查看1dB压缩点:

输出1dB压缩点要选择输出端口:(输入功率为-60--- -10dBm)

也可以将Format改为Power Gain来得到相同的结论。

还能查看单周期的情况:

测量三阶互调点IIP3

对于源端口而言,这里的PAC用以设置功率相同的另一个信号

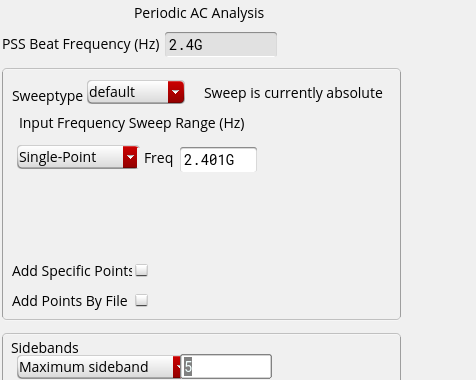

这个时候还需要进行pac仿真:

设置1MHz的频偏进行仿真,这里是叠加在大信号上面的小信号运算:

这里的边带数要大于3!

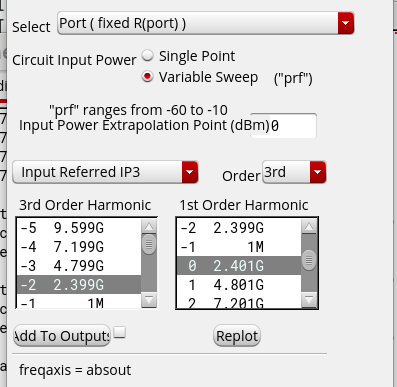

这里选择-50dBm的输入下限,并且因为基频分量是2.401GHz,

所以对应的三阶分量:

得到三阶交调点:

这里不使用采取在输入port当中双音信号是因为其仿真速度可能会很慢并且难以收敛!

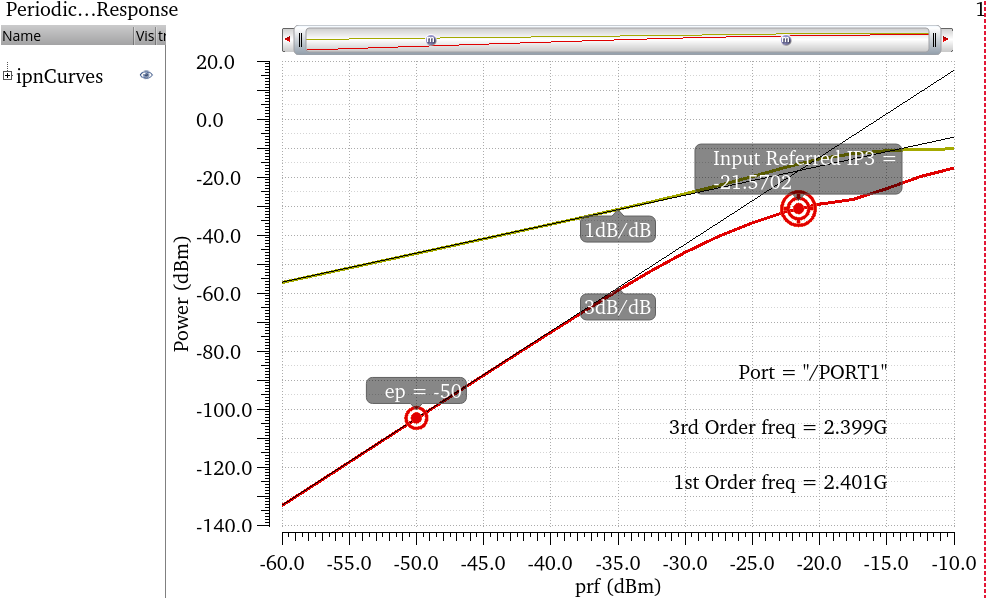

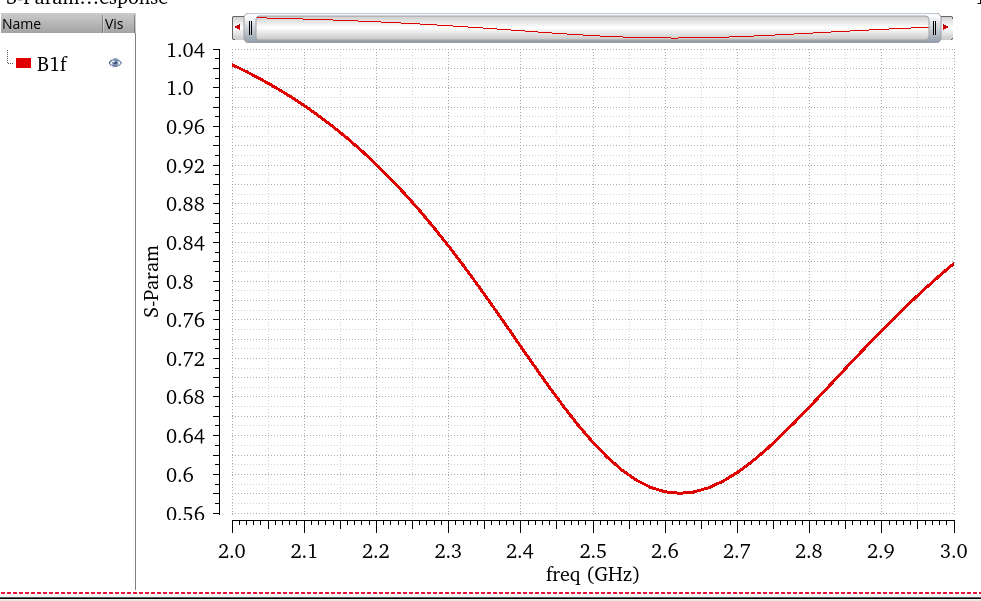

使用s参数仿真进行稳定性分析

在实际仿真时尽量把频带设置得宽一点!以免LNA在高频段出现振荡的情况。

这里的

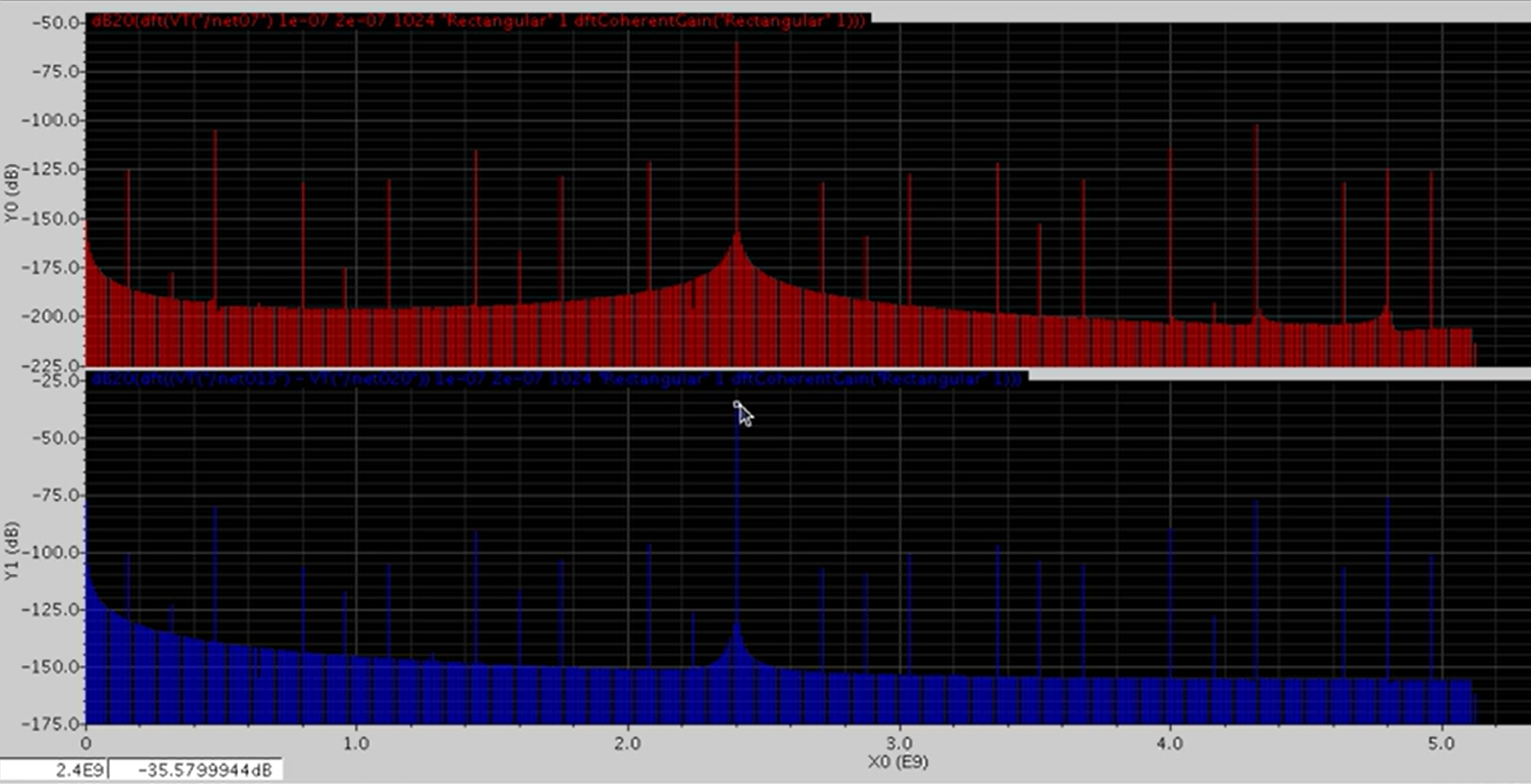

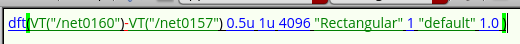

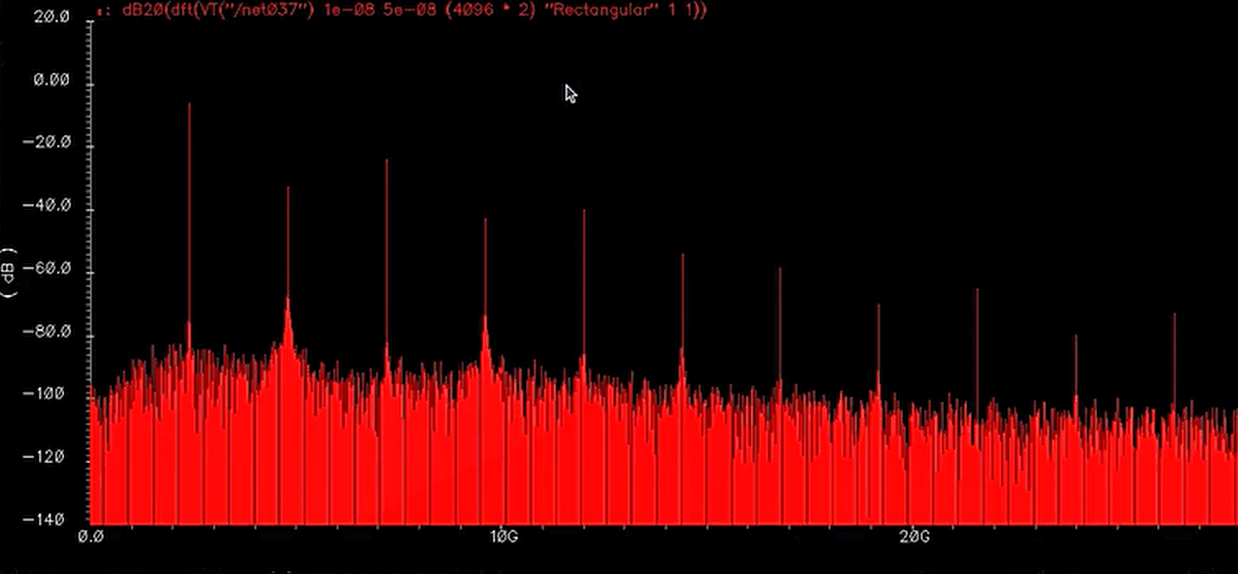

使用dft对于输出的时域波形进行运算。

如果电压(dB)折算到50欧姆的负载上,则直接+10dB得到输入功率。

也可以通过这个方式计算输入的1dB压缩点

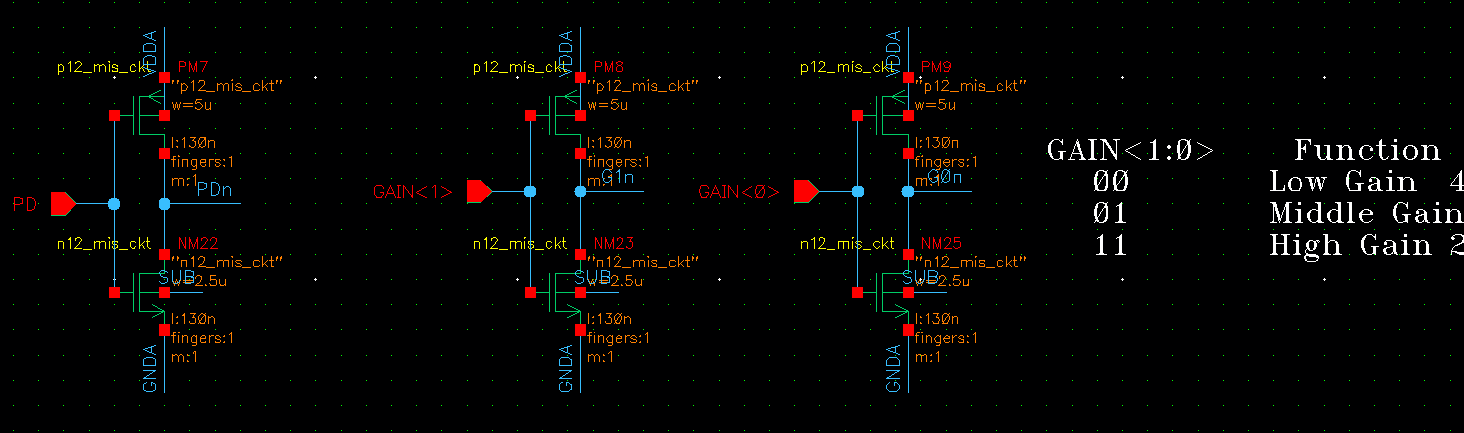

LNA的增益控制设计

改变跨导(W/L,ID),负载阻抗值,采取开关进行分流,负反馈增益控制(运放的负反馈结构?)

改变共源管的尺寸、负载电阻(减小一半)观察增益的下降以及噪声的恶化情况。

如果改变输入管的尺寸,那么其电容

改变工作电流,对匹配的影响不大,但会影响线性度

改变负载电阻,较常见,不影响工作电流,但是影响摆幅,影响1dB压缩点

采取深度负反馈的方式!在源极串联电阻/或者在漏端并联电阻(会影响直流工作点!那么就在反馈路径上串联一个大电容!而且由于已经存在了耦合电容形成差分信号,那么可以直接利用这个电容)到栅极。

这个时候增益会降低,噪声系数会恶化,输入匹配会恶化,线性度会提高,输入阻抗会提高

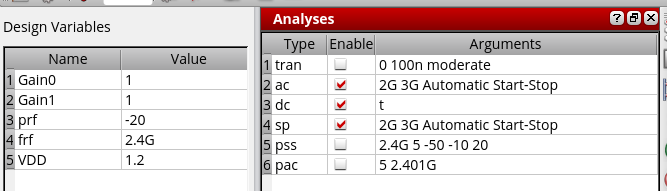

工艺角仿真

tt状态下:

-40°

25°

采取不受温度影响的恒流源,而非恒压源,减小温度的改变造成的巨大影响!

记住每种状态要查看dc直流工作点是否有巨大的偏差!!!

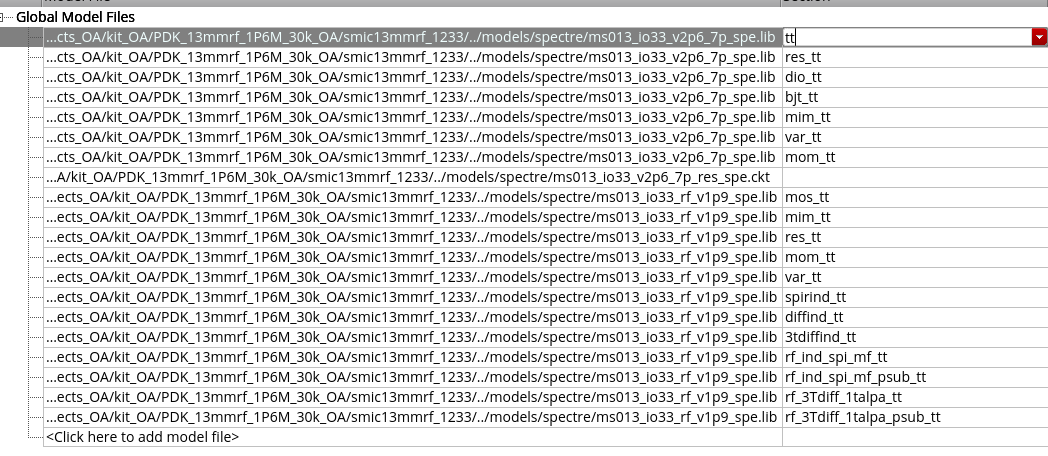

工艺角仿真时记得改model lib!

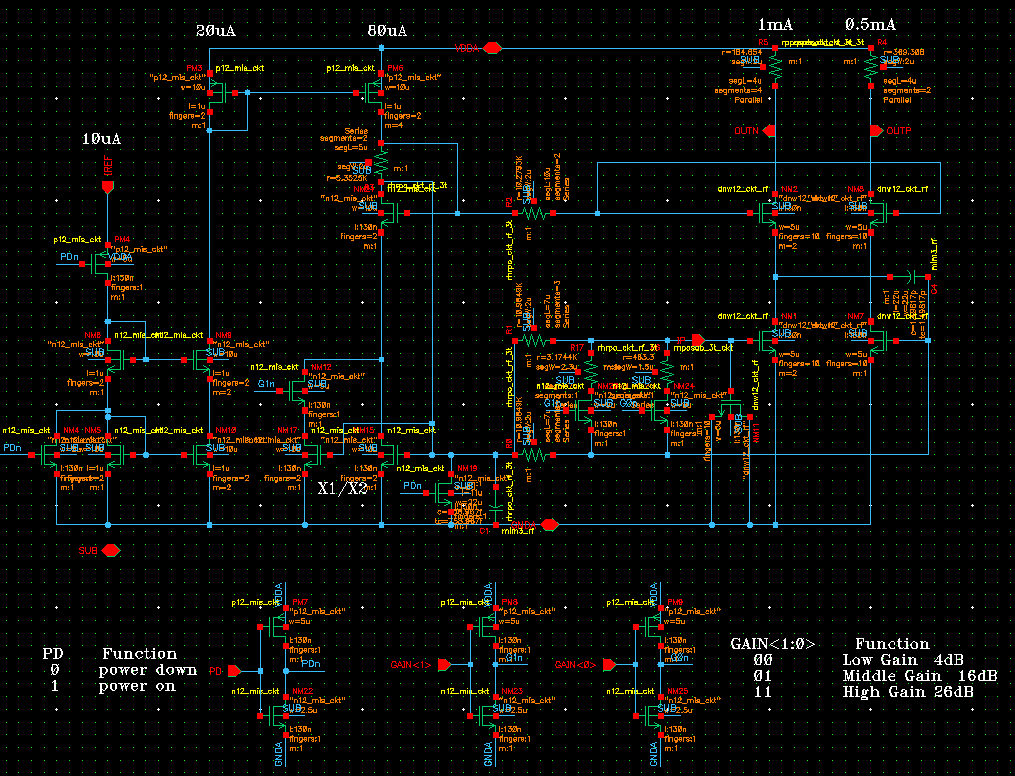

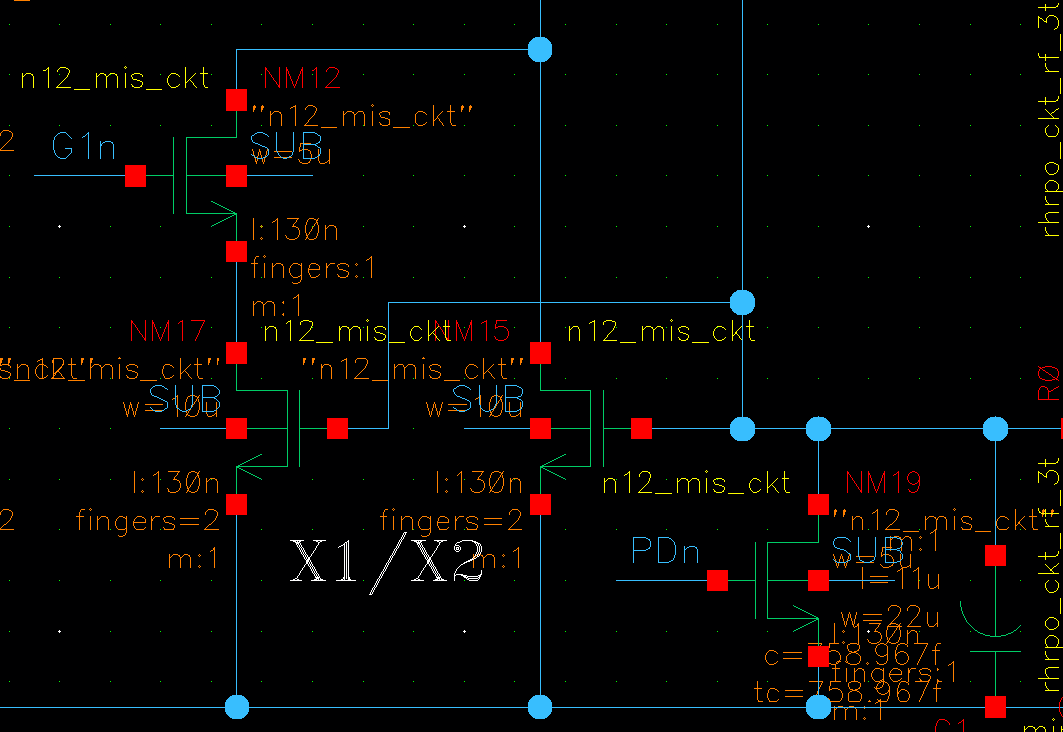

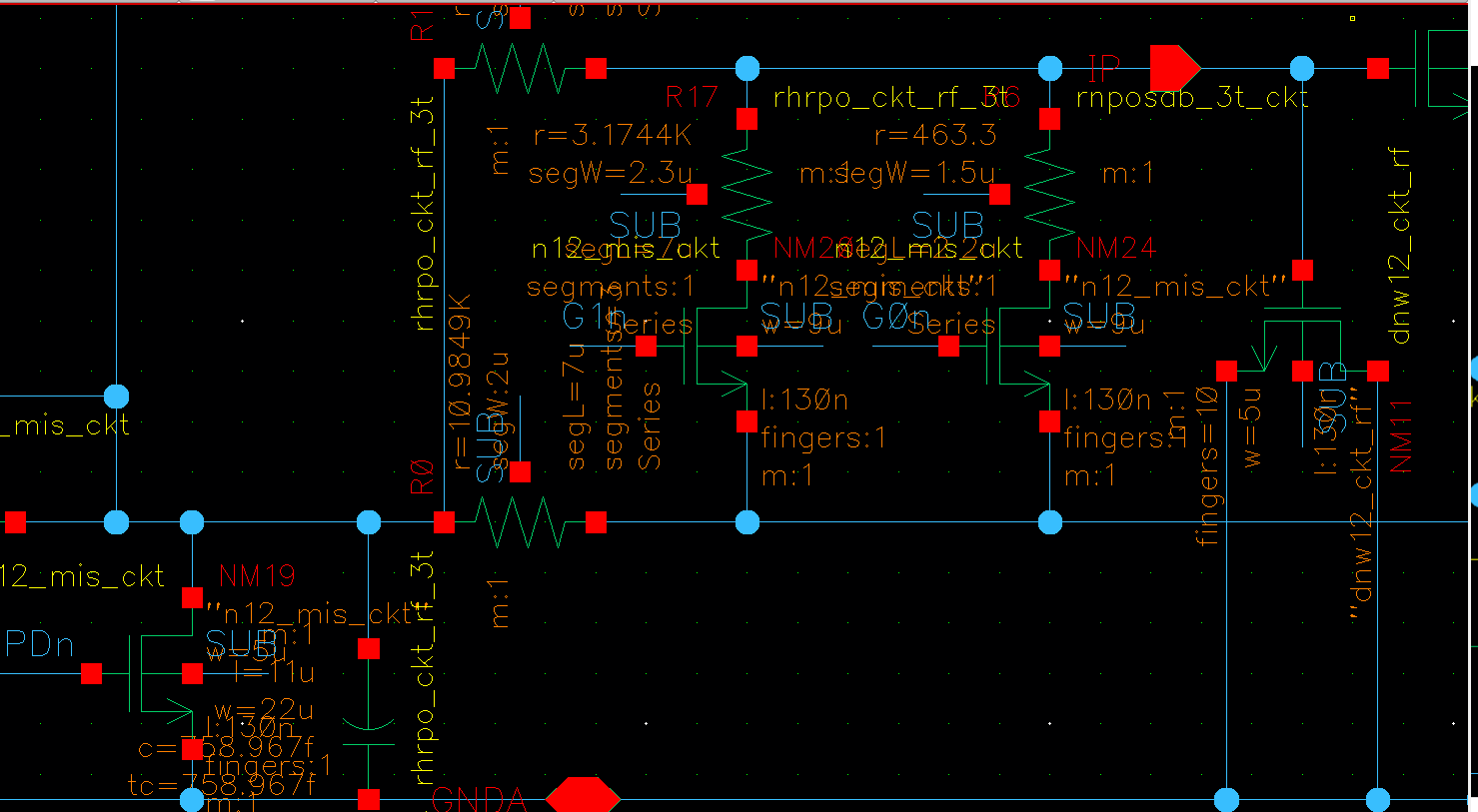

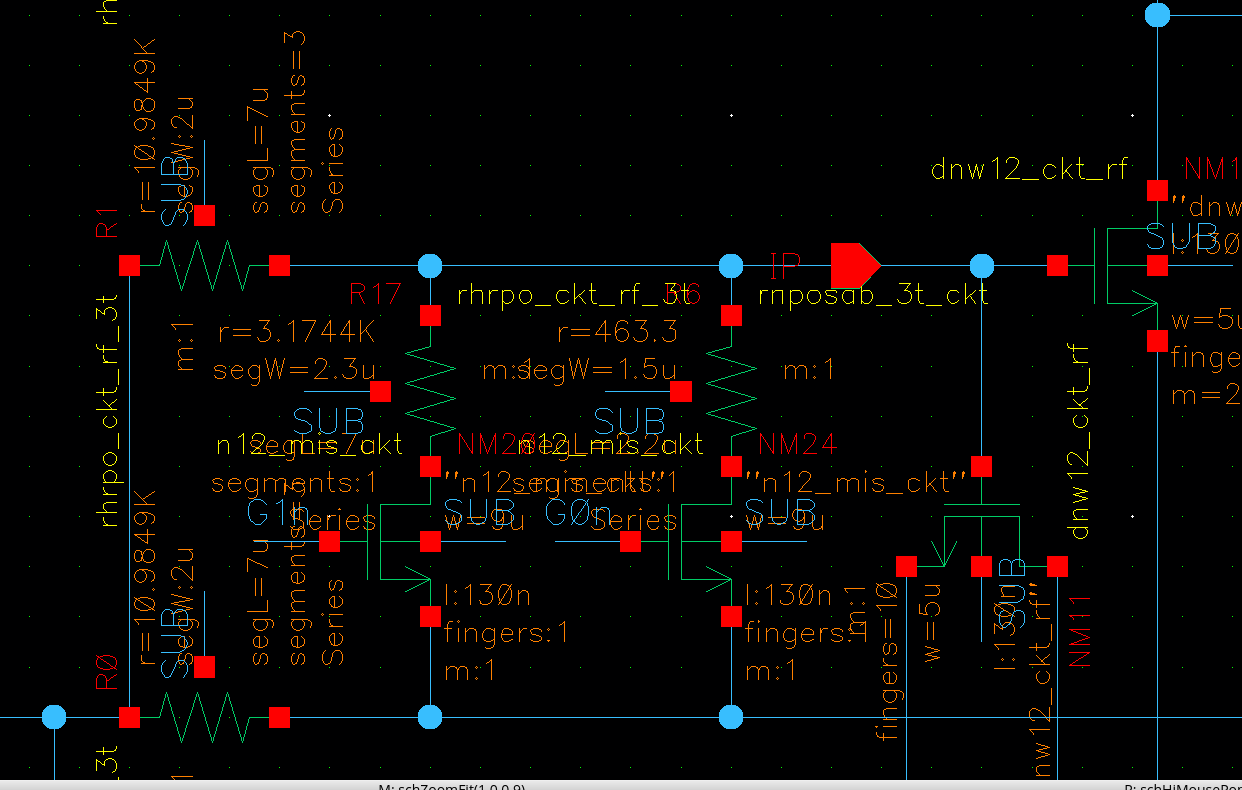

LNA完整电路设计以及蒙特卡洛仿真

外部参考电流

这里的外部参考电流是由带隙基准电压+运放形成的golden current = 10uA

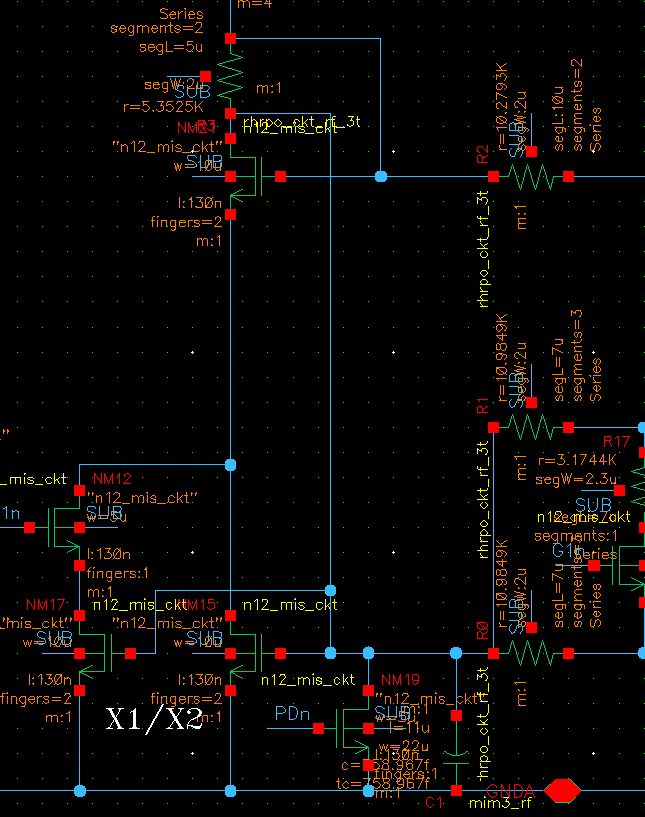

注意到这里使用了两次电流镜。开关使用的是小尺寸的PMOS,下方使用层叠型电流镜,这样的电流镜像准确度更高(cascode,见Razavi电流镜一章),再通过PMOS镜像电流到80uA,将此电流作为核心电路的偏置。

在这里并没有采取左边的二极管接法,因为这样会导致NMOS管的漏极电压过高(>过驱动电压)

采取串联电阻的方法。这时的电阻两端的压差相当于

另外,核心电路的共栅管的偏置由电阻下方的MOS管的栅极电压提供:

另外这里设置的开关是为了改变电流镜的并联个数,当开关导通时,NM17管与NM15管相并联,核心电路的工作电流减小一半。

另外,NM19导通时核心电路共源管的栅极被拉至GND,电路不工作。这里的滤波电容采取0.7pF的

增益的控制采取2bit的控制电压

开关的通断与负反馈电阻有关,除此之外,开关控制上文所说的并联晶体管,以此来控制偏置的工作电流。

另外还有由MOS构成的电容,这是因为仿真得到的外部匹配电感24nH太大,意味着输入阻抗对应的电容值较小,如果在输入端口并联上一个电容增大

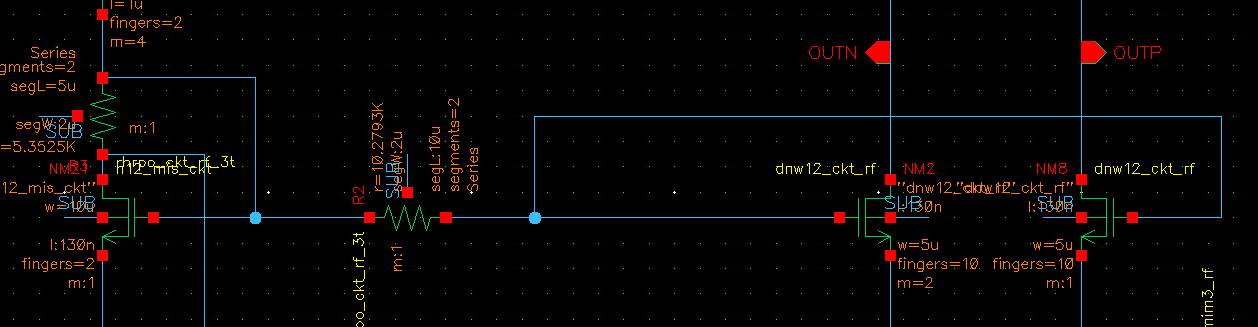

另外为了减小整体的功耗,采取手段将右半部分的直流电流减小到0.5mA,方法是将支路上面的MOS管的尺寸全部减半(并联个数减小一半),并且为了输出信号幅度相等,提高右边的负载电阻(1倍)!这里的噪声系数主要是由左半部分来决定的。

搭建testbench

设置变量

增益设置为1代表最高增益的状态

首先检查偏置电路是否提供了足够的偏置,并与理性的偏置电路比对。

其次改变工作温度,检查电路的工作性能。

工艺偏差的影响

这里的晶体管选择失配管(mismatch),注意将其标志位设置为1

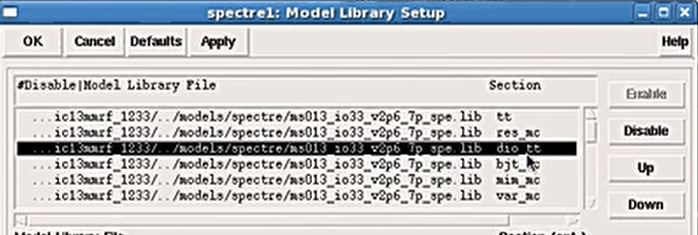

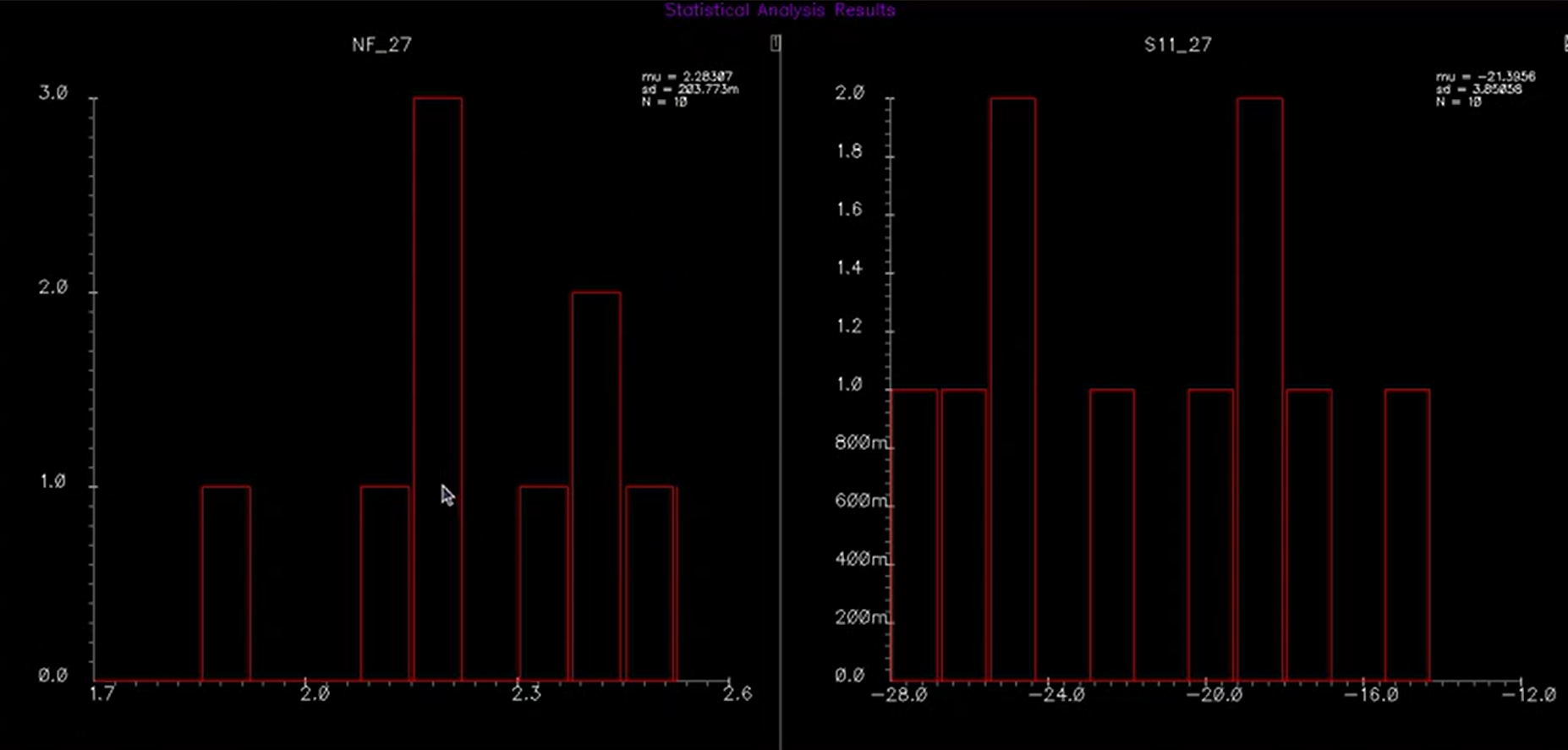

然后进行蒙特卡洛仿真(后缀为mc的模型)

注意仿真mc模型的重复包含(重复定义)造成的偏差

仿真10次,Analysis Variation 选择 process & mismatch

这里的表达式可以填入噪声系数的表达式:

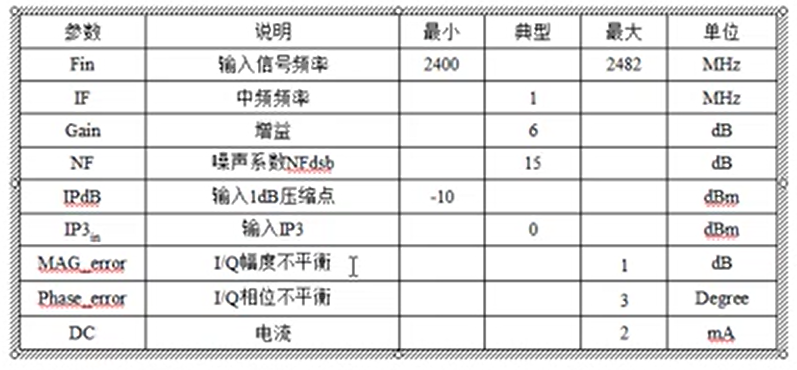

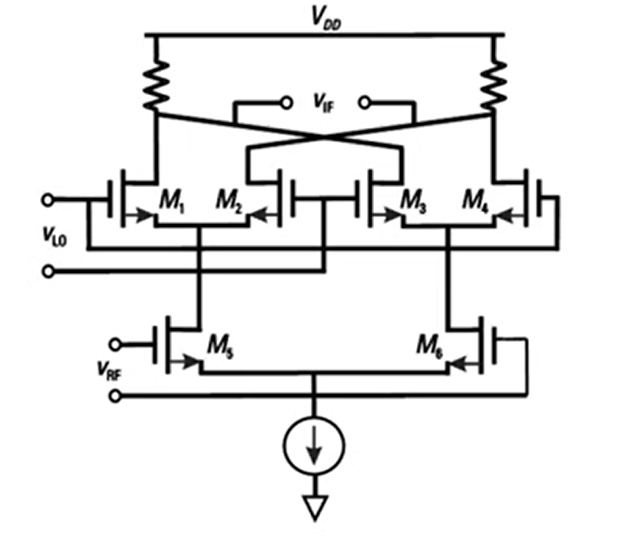

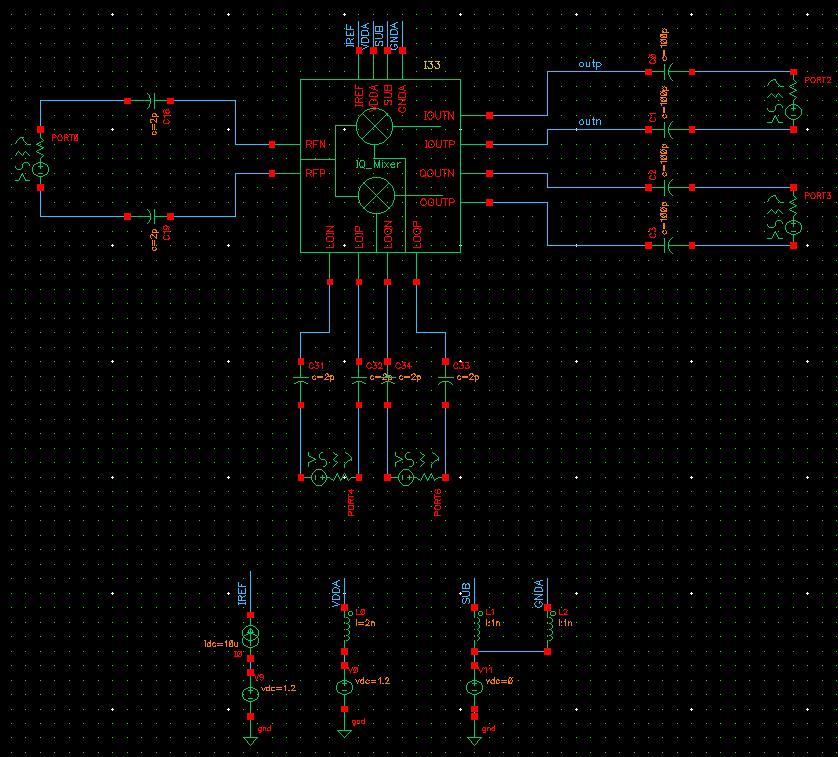

Chapter Ⅲ I/Q混频器

电路结构以及原理图设计

调节本振的偏差来调节幅度和相位的不平衡性。

跨导级---开关级(本振信号驱动)

尾电流源的意义:输入阻抗很高,抑制共模干扰信号

要产生正交信号,还要加一组正交电路。

为什么不采用尾电流源?消耗电压裕量(电压摆幅受限),并且线性度不好。(牺牲了共模抑制)

注意跨导级输出的接法!!!

偏置电压:偏置跨导级和开关级,偏置电路和LNA是相同的。

偏置电阻设置为

最先确定的是跨导级的尺寸----要满足输入极低噪声的特点;其次工作电流要小于2mA,再者线性度要最大化,其工作电流要最大,约为2mA(单个跨导级1mA)

跨导级要工作在低噪声状态!

为什么并联2个?版图交叉匹配

开关管的尺寸:为什么不设置为最小沟道长度?

考虑到

为什么尺寸比跨导级小?跨导级的电流会流入4个开关管,同时希望开关晶体管开关特性好,小尺寸寄生电容较小,更好驱动,功耗更好,但是问题是导通电阻会增大,并且因此会带来较大的热噪声

负载电阻越大,变频增益越高,但是相应的电压降会增

加!(每个0.5mA的电流,并且开关管漏极的电位要比栅极电压高(

输入阻抗给100Ω(因为是差分的源阻抗),信号源输入设置:

小信号的功率值及其相位分别进行设置!

还要注意的是,I路和Q路的本振信号要加入2pF的隔直电容!

通常本振提供的信号为0dBm,设置I路的相位为0,频率为2.4GHz,摆幅初始设定为200mV,

Q路的相位为90,频率为2.4GHz,摆幅初始设定为200mV

负载阻抗设置为10kΩ,偏置电流设置为10uA,为混频器提供恒定的偏置。

在仿真中,设置射频信号

首先进行dc仿真

一定要确定跨导级工作在饱和区!!!一般比

结果是,总的电流是

确实工作在饱和区,并且工作电流在

先进工艺下,

0 cut-off 1 triode 2 saturation 3 sub-threshold 4 breakdown

增益以及噪声仿真优化

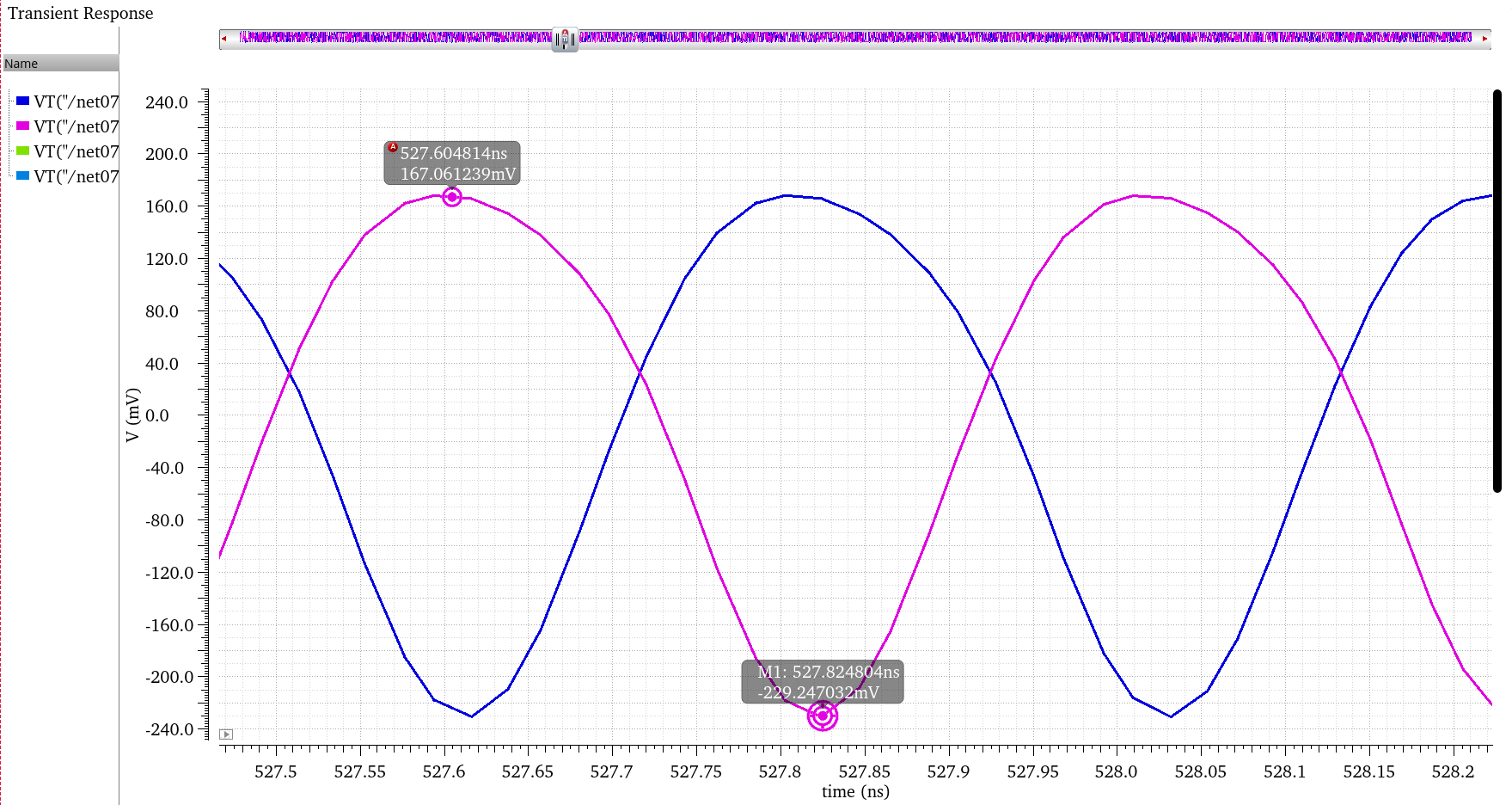

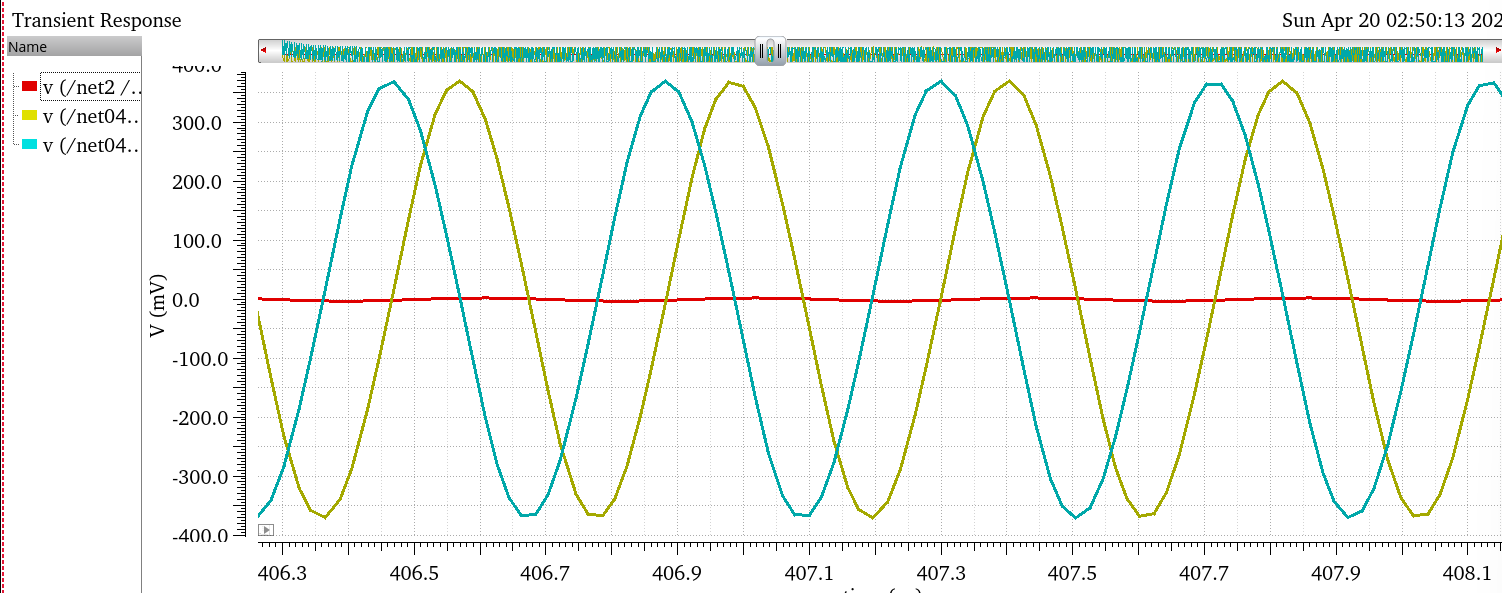

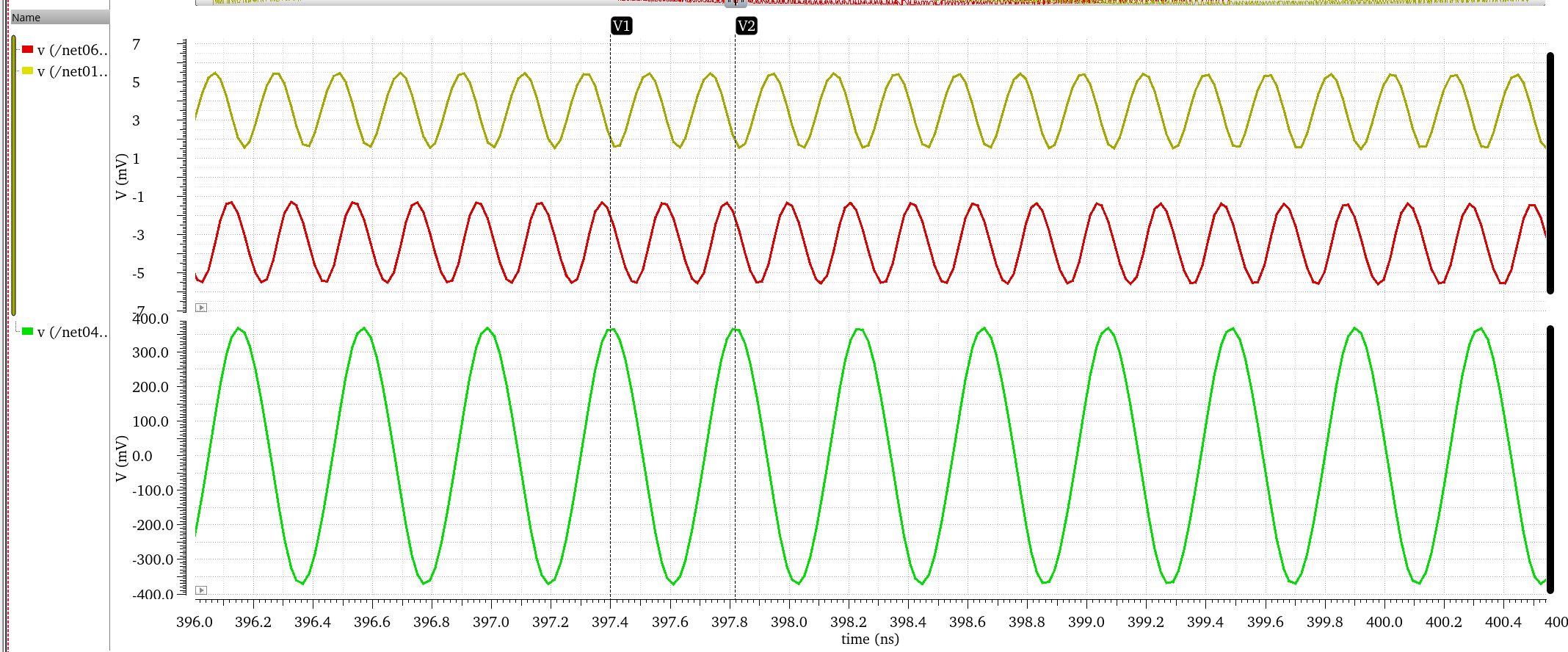

首先查看瞬态波形,利用trans仿真,首先查看本振信号的波形:

可以看到单端的

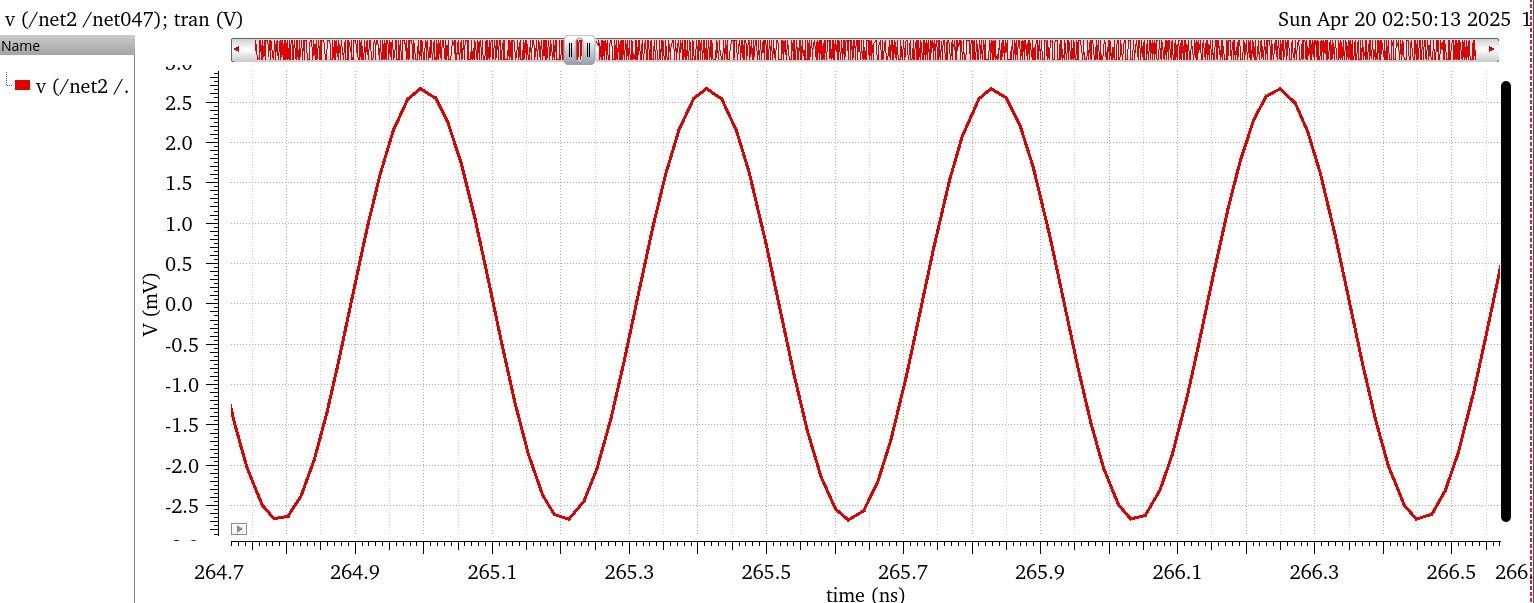

然后查看射频输入2.401GHz信号的波形(-50dBm):

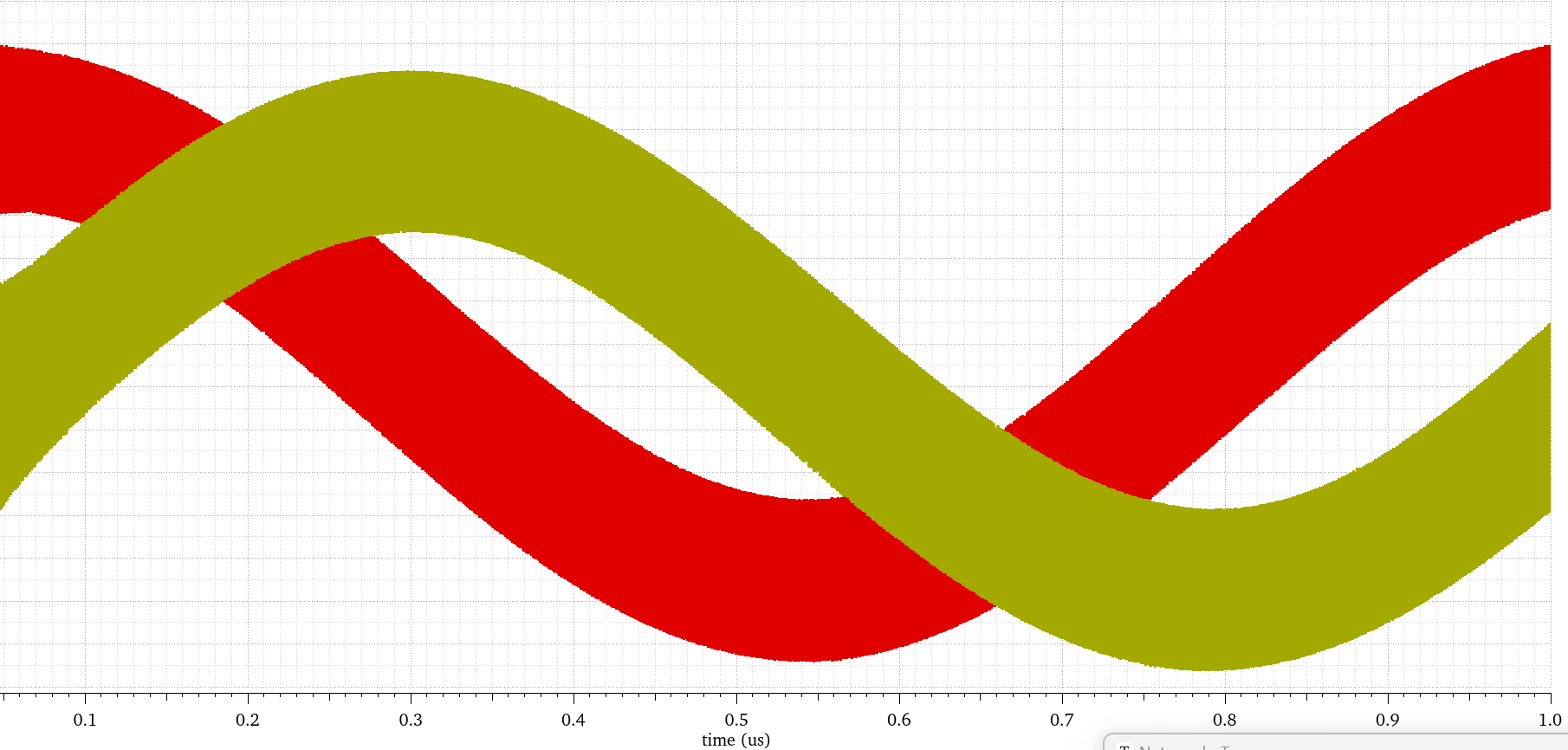

查看输出Q路与I路的波形如下图所示,注意开始时会有一段建立时间

这是因为叠加了2倍频率的本振信号,放大查看波形:

将本振差分信号与输出的信号作对比:

发现输出波形的确包含本振的2倍频泄露分量。

消去泄露分量的方法是,加入比较小的滤波电容,或者在输出信号当中加入带通滤波器

查看线性度时,应查看单端的波形(包含共模信号的影响)

首先要查看跨导晶体管的栅极和漏极的波形,观察其是否进入线性区进而失真

其次是要观察开关级晶体管是否因为本振信号的摆幅过大而进入线性区。

也即:查看

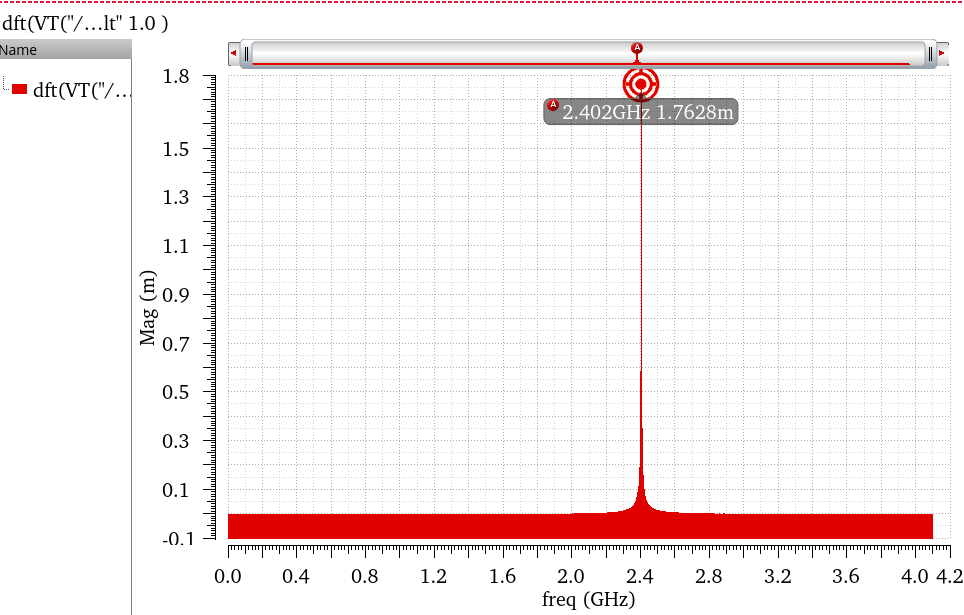

进行频谱分析:

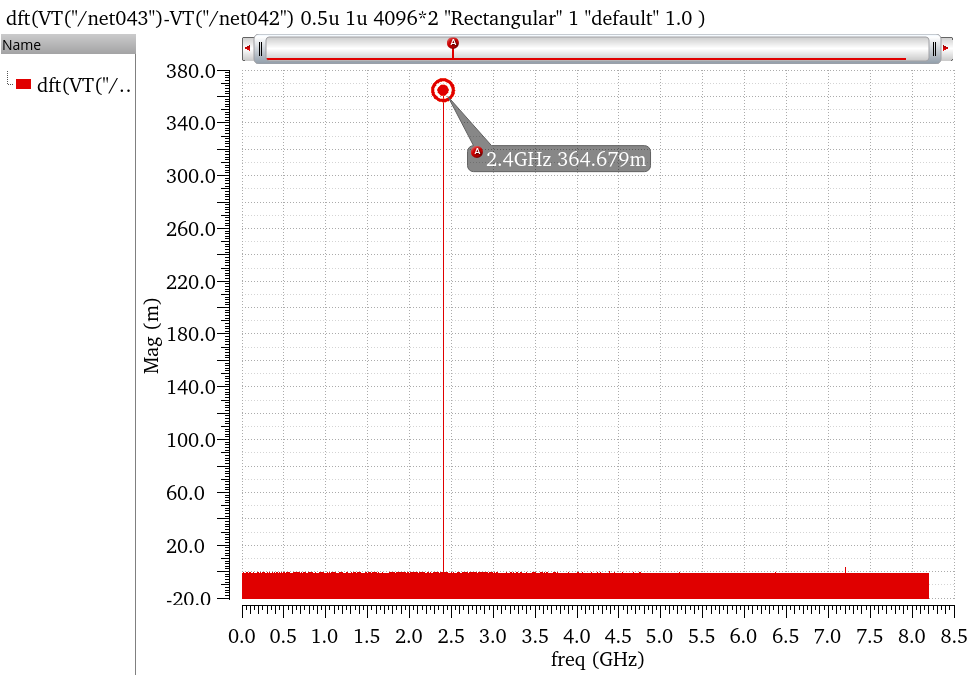

首先查看输入的差分射频信号的频谱:

输入的射频信号频谱:

输入的本振信号的频谱:

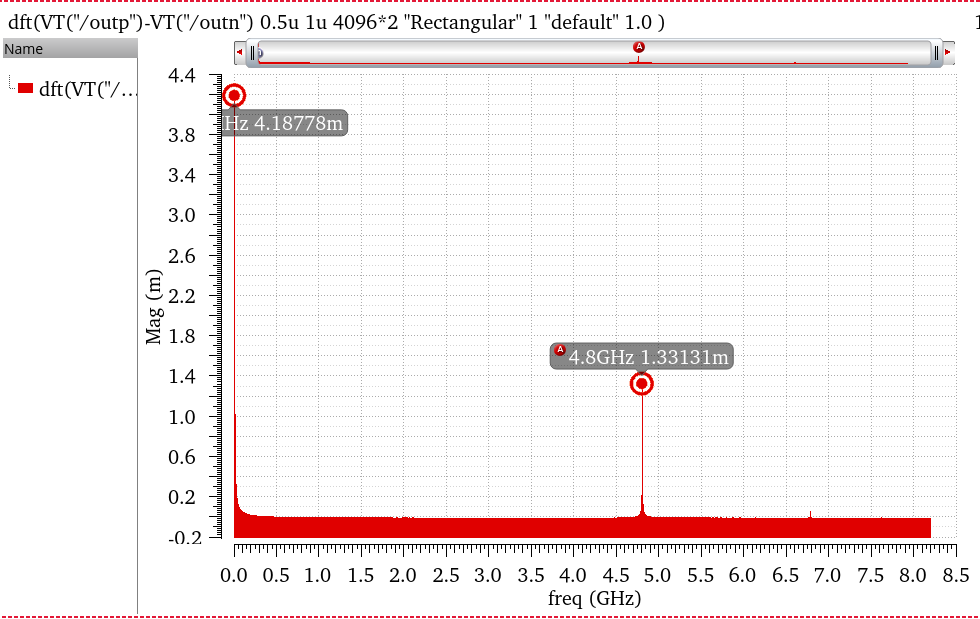

输出的中频信号频谱:

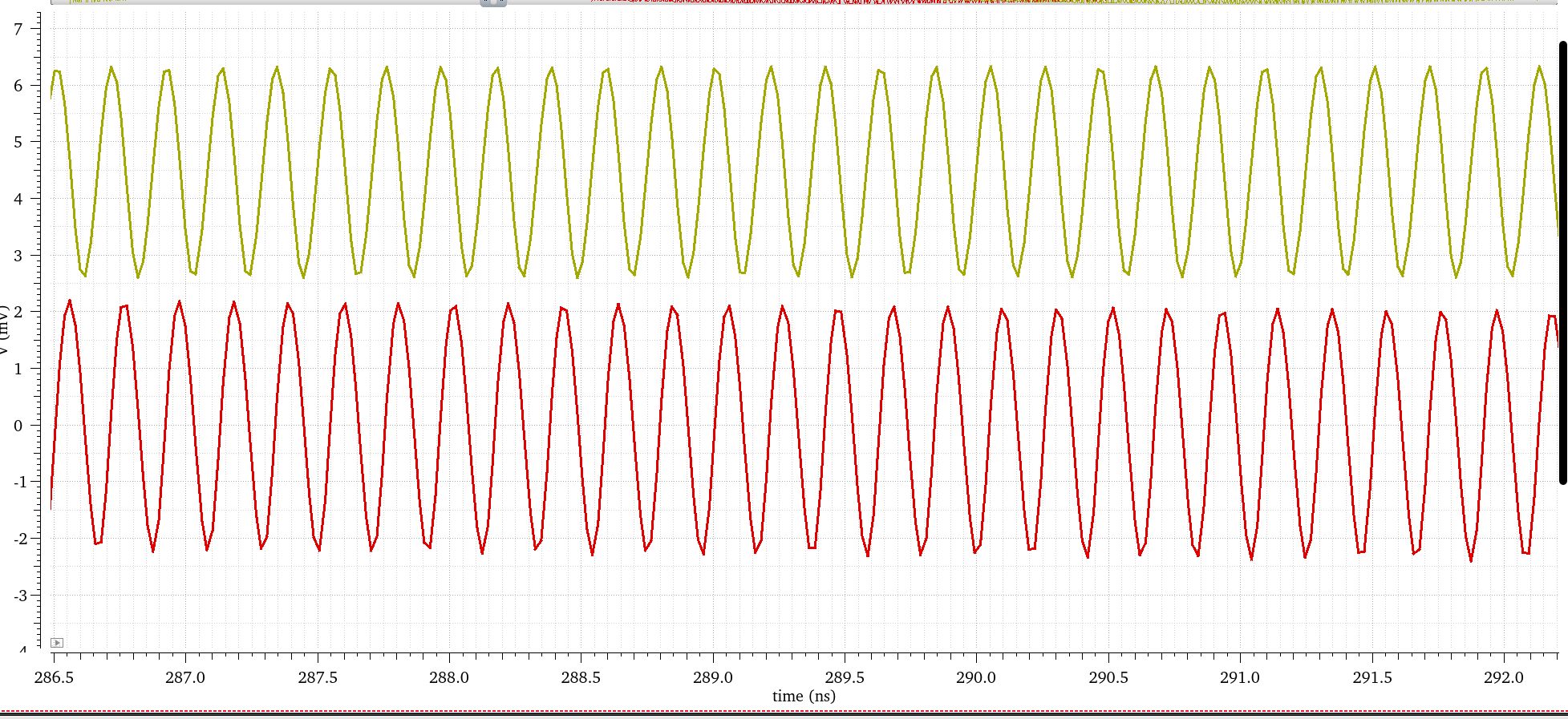

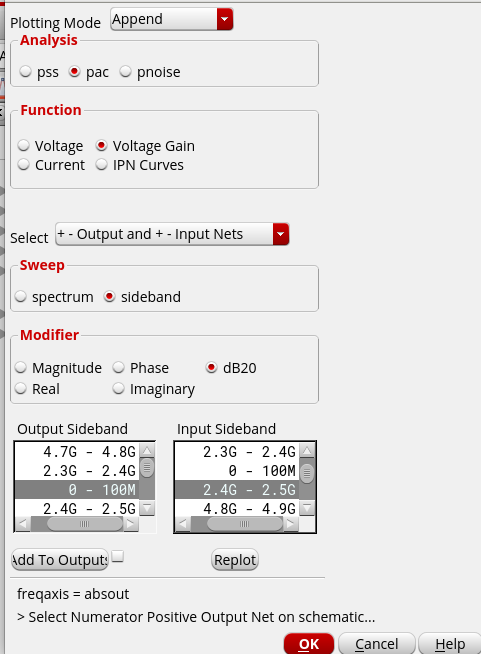

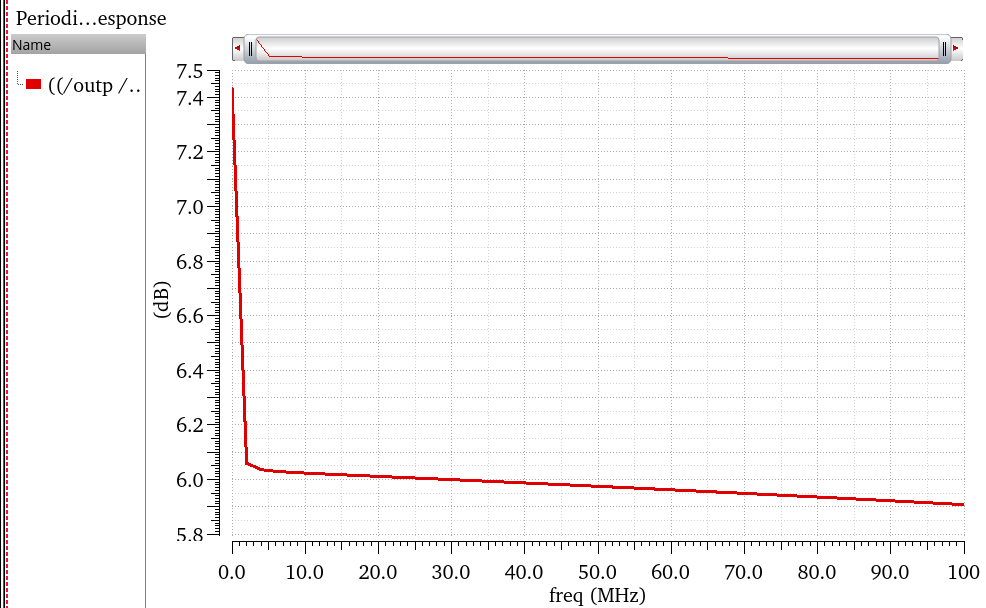

通过查看本振输入信号(2.4GHz)的功率与中频输出信号(1MHz),得到对应的增益,根据上图推算大约在6dB左右

使用pss对混频器进行增益仿真

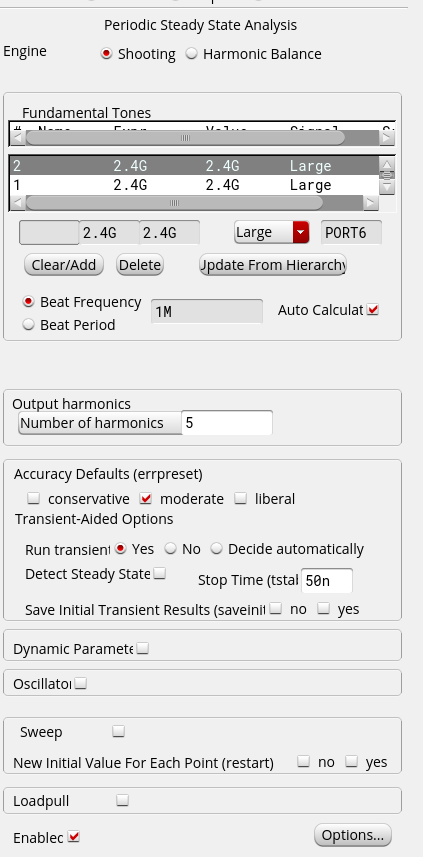

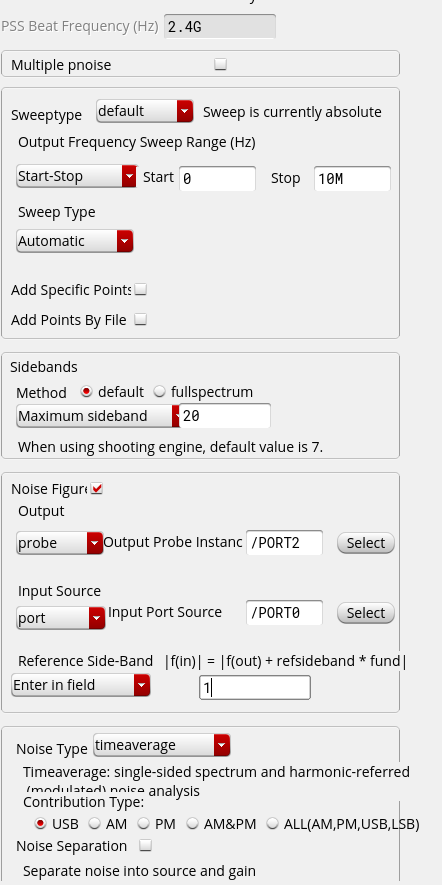

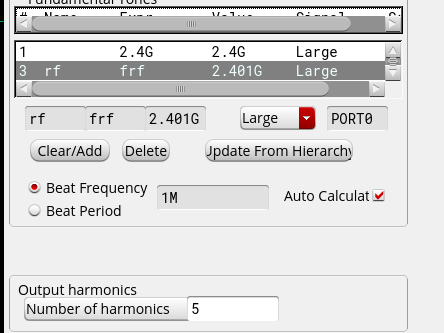

首先使用pss得到电路的大信号工作点(此时要将射频输入端口设置为dc型),在此基础上再叠加小信号使用pac进行仿真。仿真噪声时候也需要首先仿真pss,得到周期稳态响应,再叠加pnoise

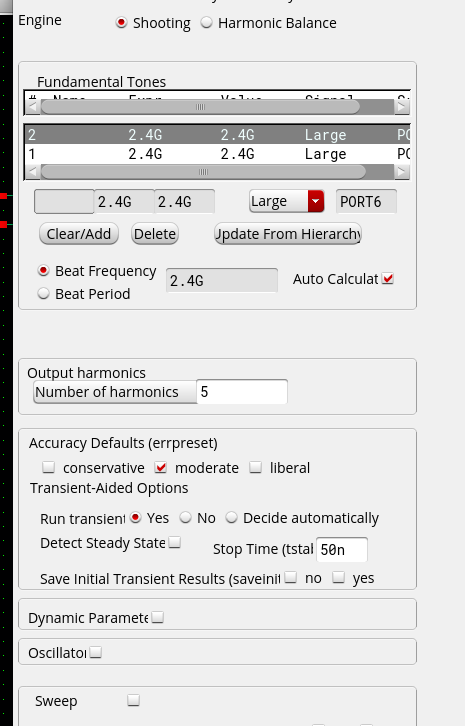

在这里,选择shooting,Fundamental Tones是大信号的本振输入。

要注意VCO一般要考虑使用Harmonic balance

在这里,选择Auto Calculate,如果将射频输入端口设置为正弦输入,那么就是2.401GHz,

那么二者的最大公约数会被设为1MHz,那么要计算2400次谐波!这就是为什么要设置得dc

下方的Output Harmonics 只是显示输出的波形,实际上全部都会计算!

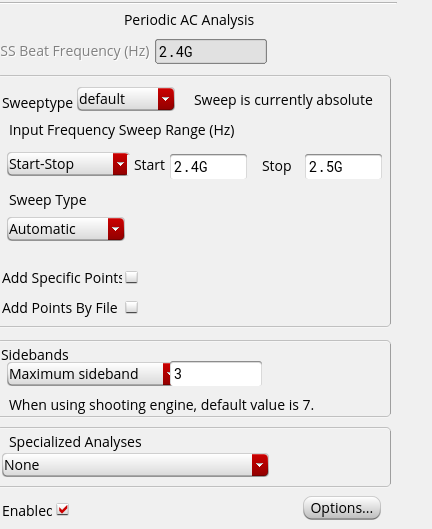

再设置pac仿真,在这里设置射频输入信号为2.4GHz-2.5GHz

在这里还要设置射频输入端口的小信号:

设置噪声仿真时。设置的是中频输出信号噪声的频率

在这里的Reference Side-Band要特别注意,设置为1代表输出噪声频率为本振信号的频率加上上方设置的Sweep Range,设置为-1则是相减

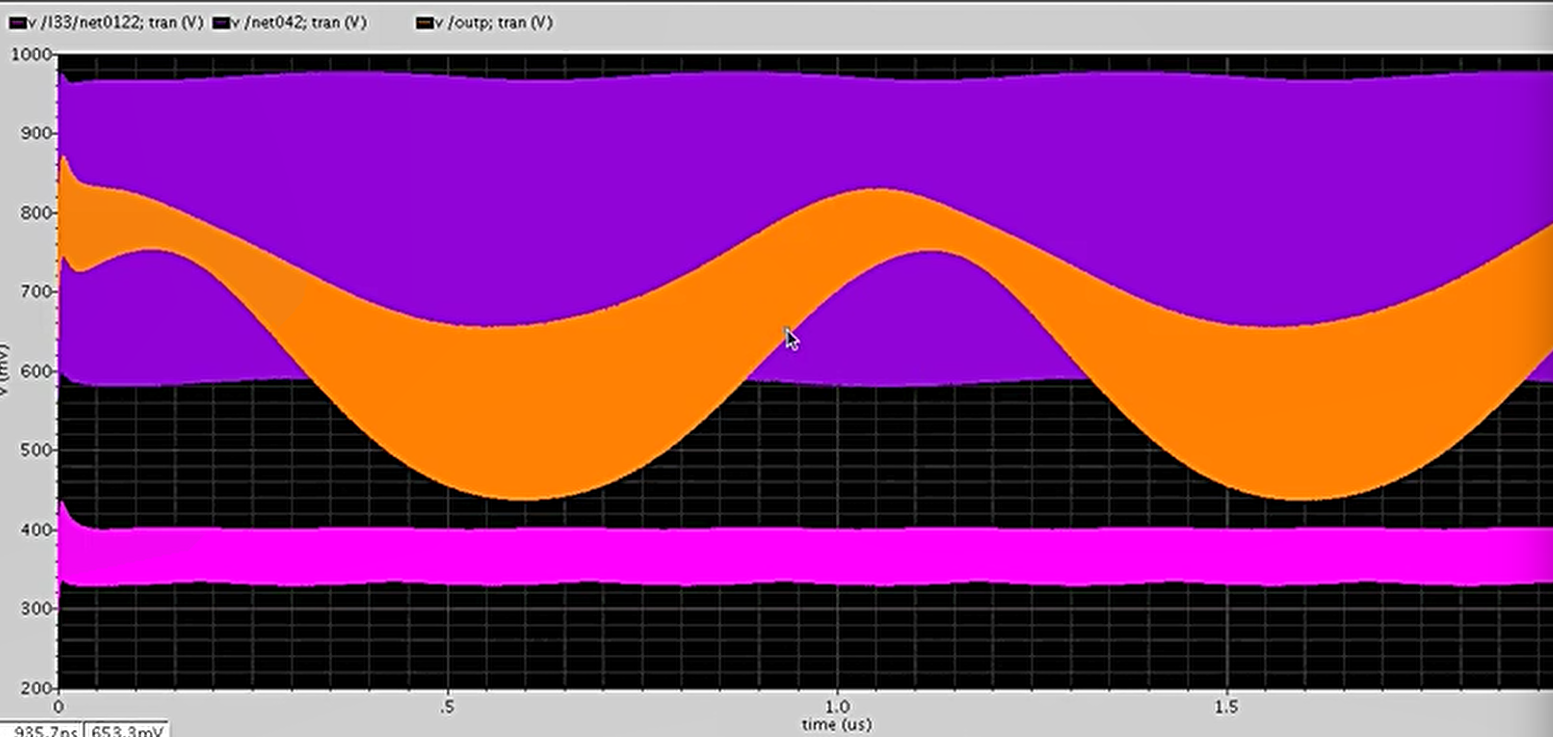

首先可以查看PSS仿真的周期稳态波形,以及对应的频谱:

使用pac---voltage---spectrum查看输出的频谱,由于混频器自身的输出性质,频谱很凌乱:

查看变频增益:

选择输入信号/输出信号的边带

再依次选择输出的差分端口以及输入的差分端口:

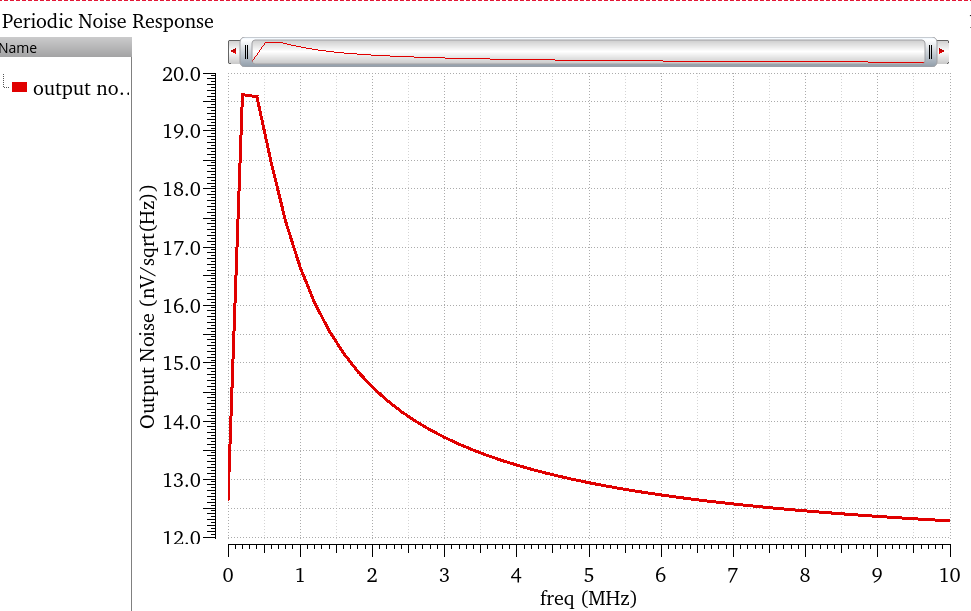

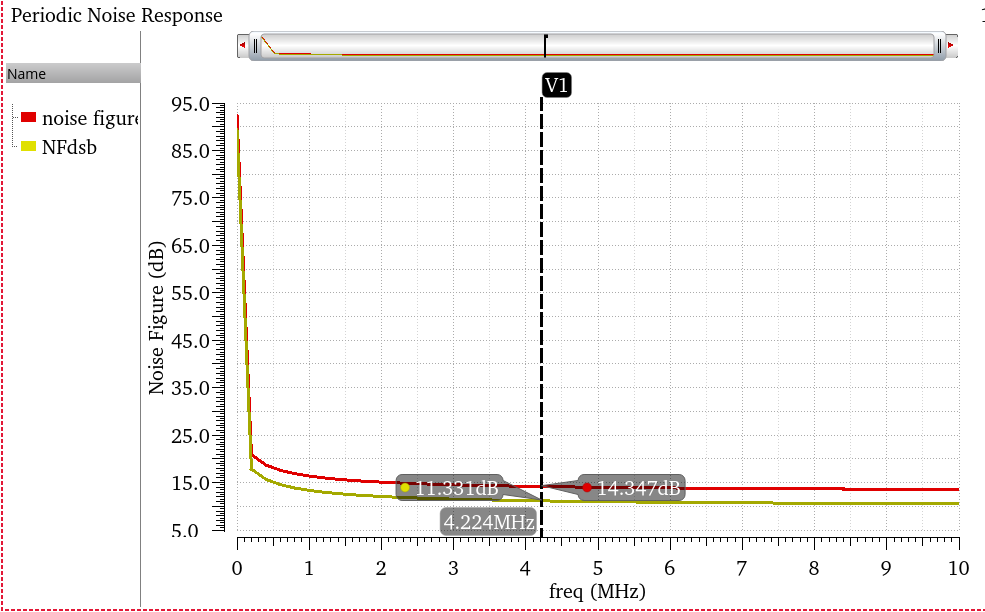

再查看输出噪声的结果:

噪声系数通常使用Noise Figure/ NFdsb,二者的差别在于,NFdsb在没有镜像滤波器的情况下,回比Noise Figure低3dB左右。

使用低中频/超外差接收链路,由于镜像频率被滤除,采取NFdsb来得到最终的结果!(此时两者的值应该是差不多的)选择Noise Summary,发现噪声大部分是由闪烁噪声导致的

大部分的噪声由开关晶体管造成,而加长开关级晶体管的沟道长度可以缓解这个指标,但是相应的电压摆幅会受很大的影响

调节增益的方法:调节跨导级晶体管的尺寸以调节电流,或者调整电阻的值得到不同的增益

线性度仿真和优化

仿真1dB压缩点

将输入的射频信号端口设置为sine类型,再设置PSS仿真:

可以看到,当设置射频输入端口为sine类型之后,beat frequency设置为了最大公约数1MHz

这可能使仿真迭代次数极多,很可能不收敛(只针对于这种低中频的混频器而言)

所以这里利用瞬态仿真是最好的!

将输入的射频信号设置为sine并且输入信号的功率从很小的功率开始累加,直至寻找到1dB压缩点

更有用的方法是利用PSS+PAC仿真出输入3阶交调点,再-10dB估计输入1dB压缩点,再由瞬态仿真验证。

首先设置三阶交调点的仿真,这里将输入的射频信号端口设置为dc类型,并且不进行sweep

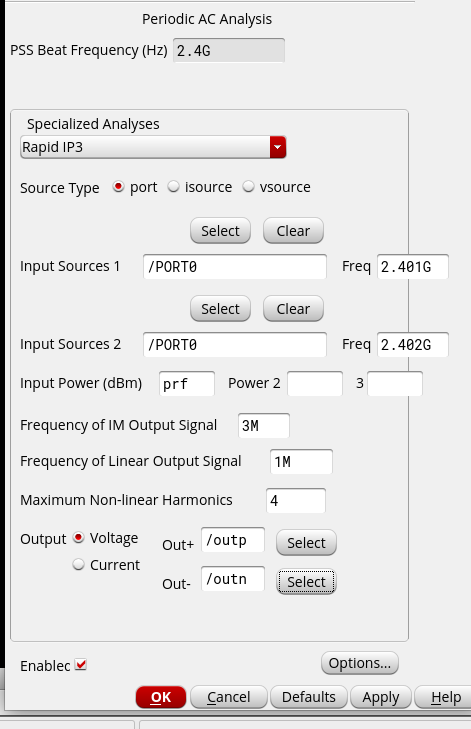

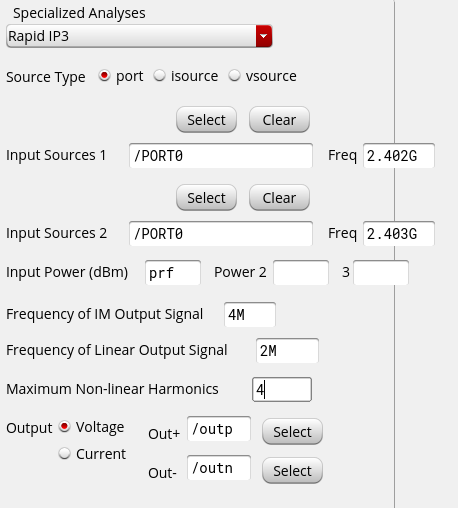

这里要设置快速设置IIP3的选项(PAC仿真设置):

在这里,选择输入射频端口的双音信号

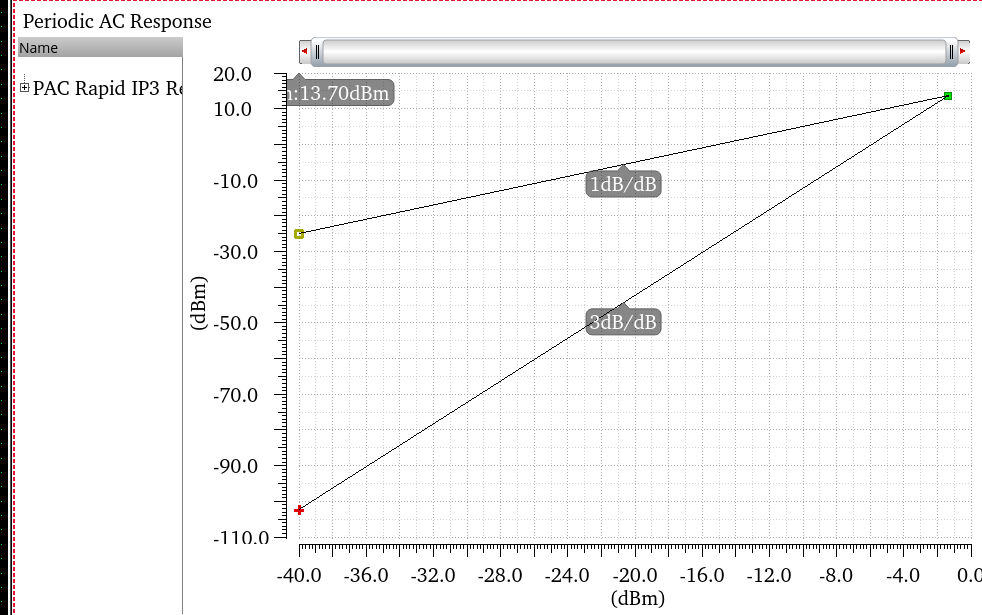

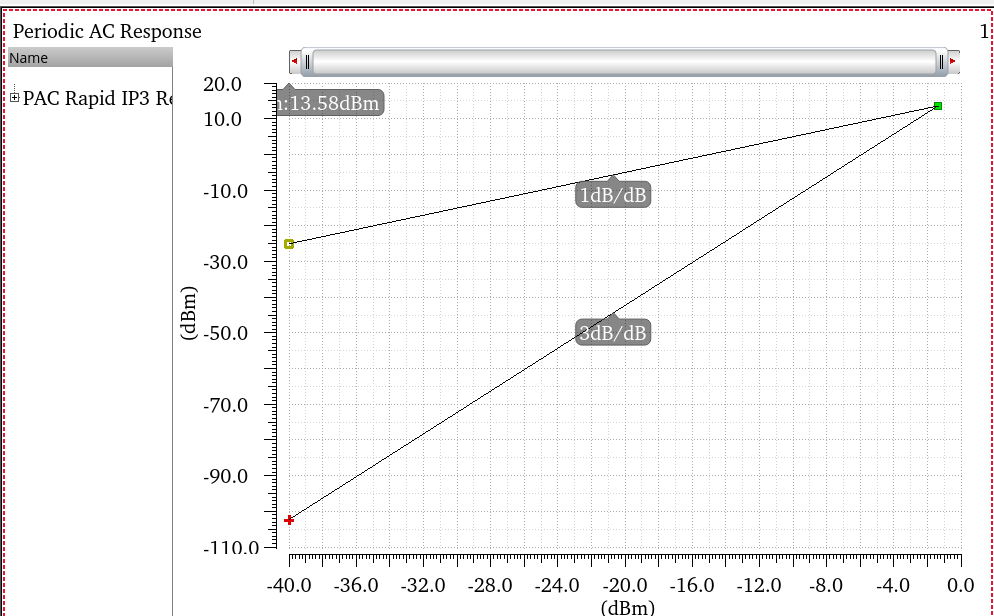

输出结果如下图所示:

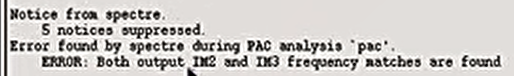

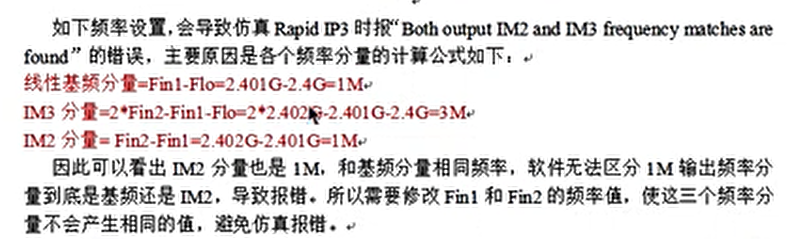

值得注意的是在ic51当中会发生报错:

二阶交调分量与有用信号的频率相同!!!

修改的方法是都加上1MHz:

可以看到输入与输出三阶交调点的值,因为输入的三阶交调点为-1.4dBm,于是再进行trans仿真(此时射频输入端口又要设置为sine类型了),此时估计输入1dB压缩点为-11.4dBm,同上一节的仿真步骤可以仿真出相应的结论。

还要进行二阶交调点的仿真方法,这种在零中频接收机当中是很重要的。

此时射频输入端口要设置为dc端口,在pac当中设置Rapid IP2即可。

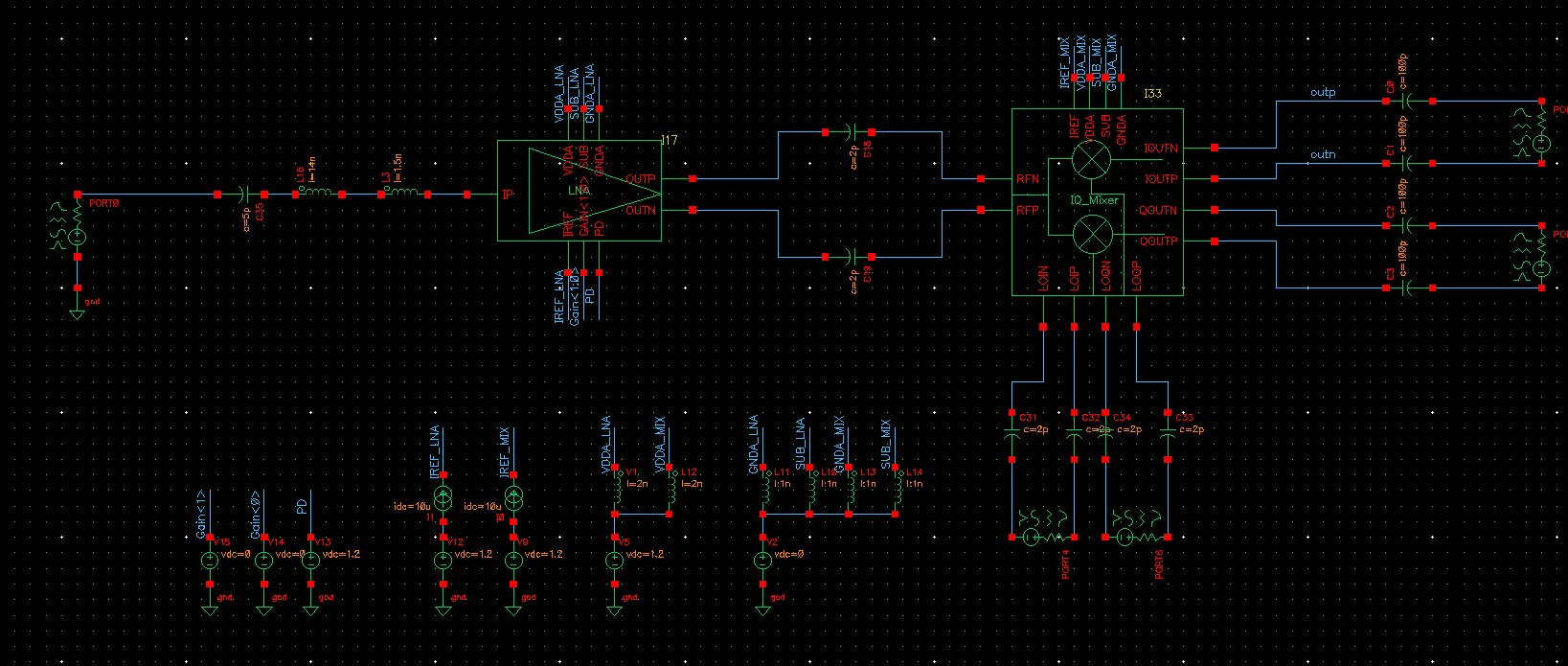

LNA和Mixer联合仿真与优化

这里的mixer没有加power down的开关。

联合仿真与单独仿真mixer差不多,首先验证S参数

查看

其它的指标如输入三阶交调点,1dB压缩点,线性度和增益等指标与上述步骤相同。

在这里调节LNA的增益(Gain端口),可以改变上述的指标,从而达到可变增益的目的。

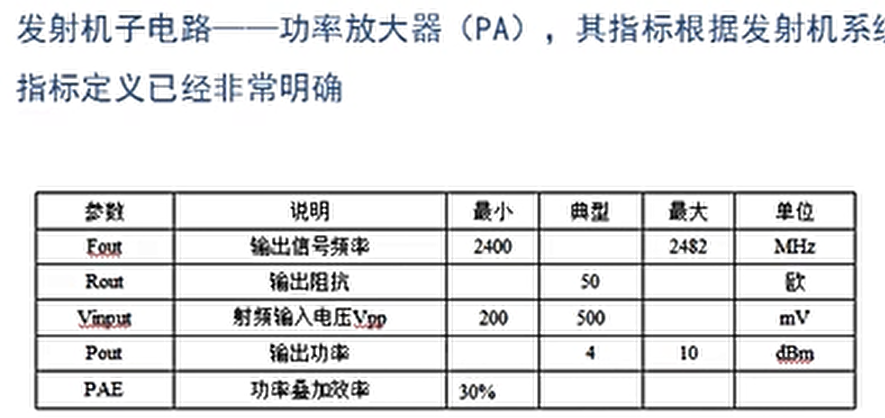

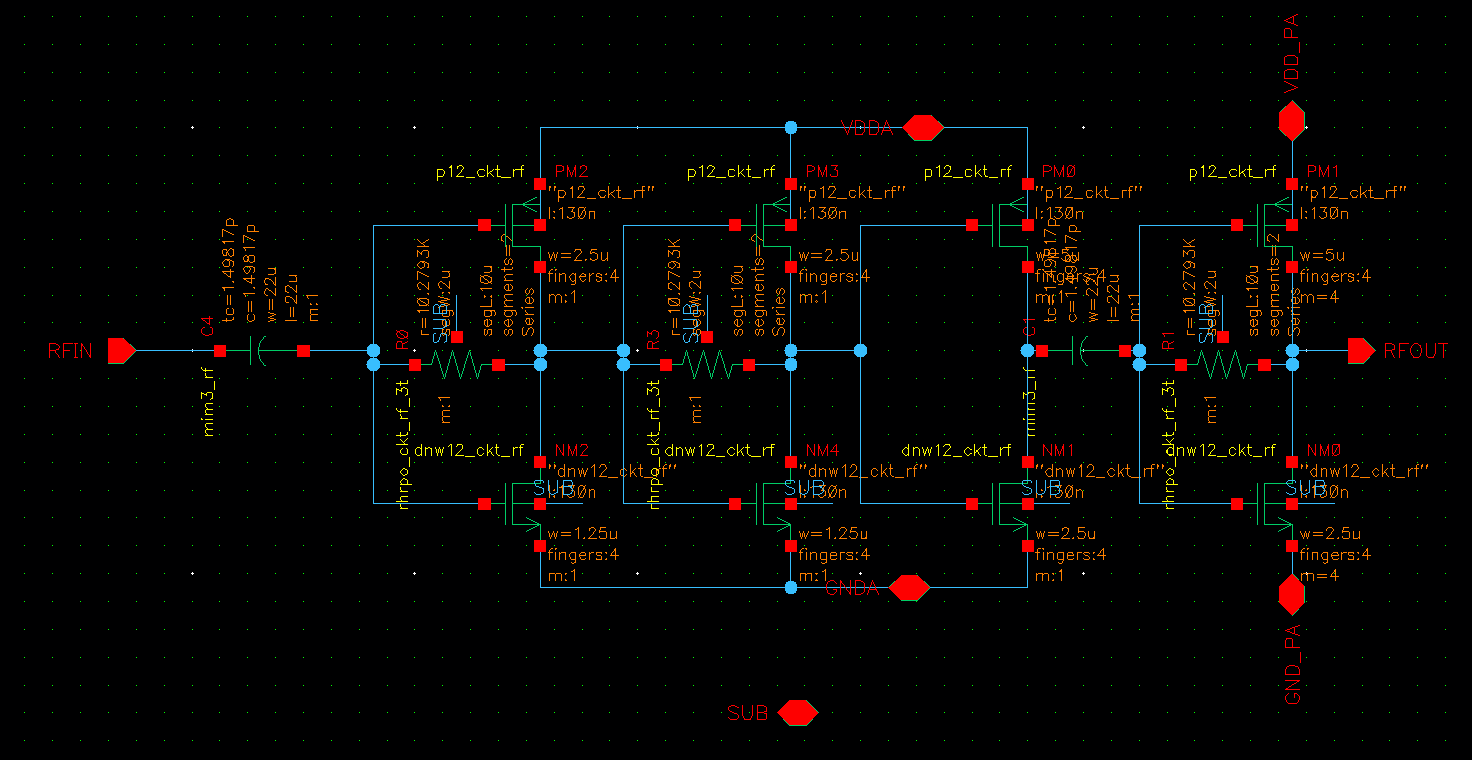

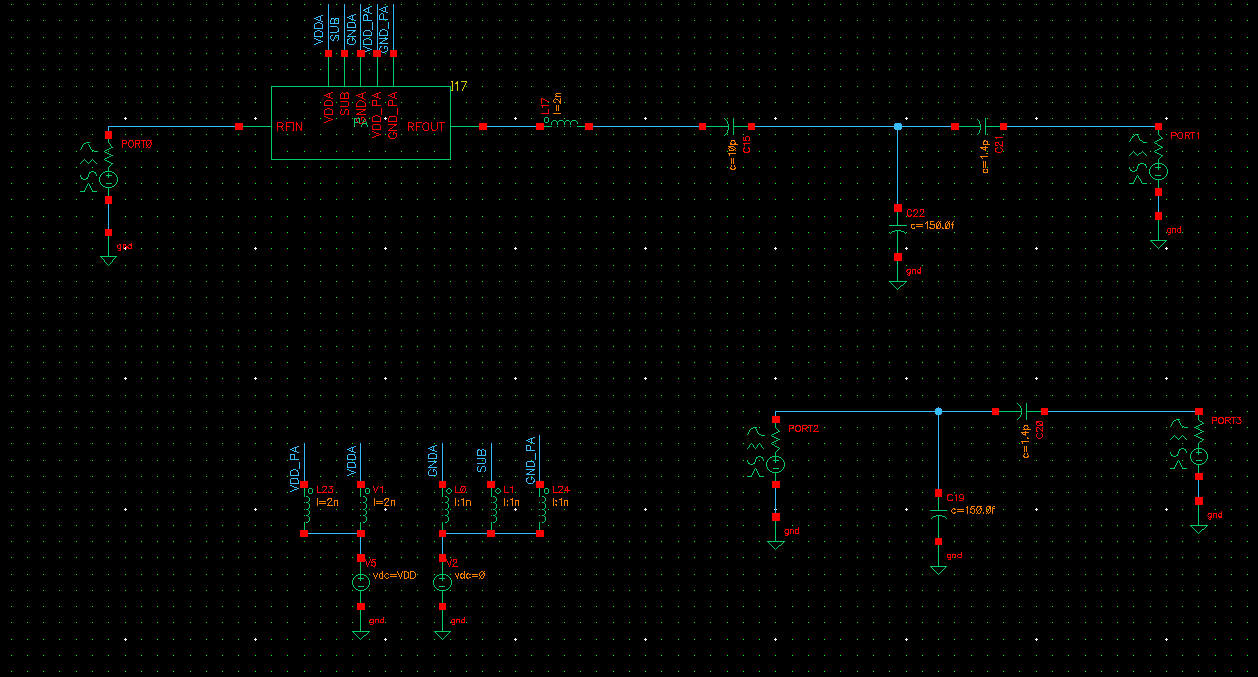

Chapter Ⅳ PA电路设计以及Load-pull仿真优化

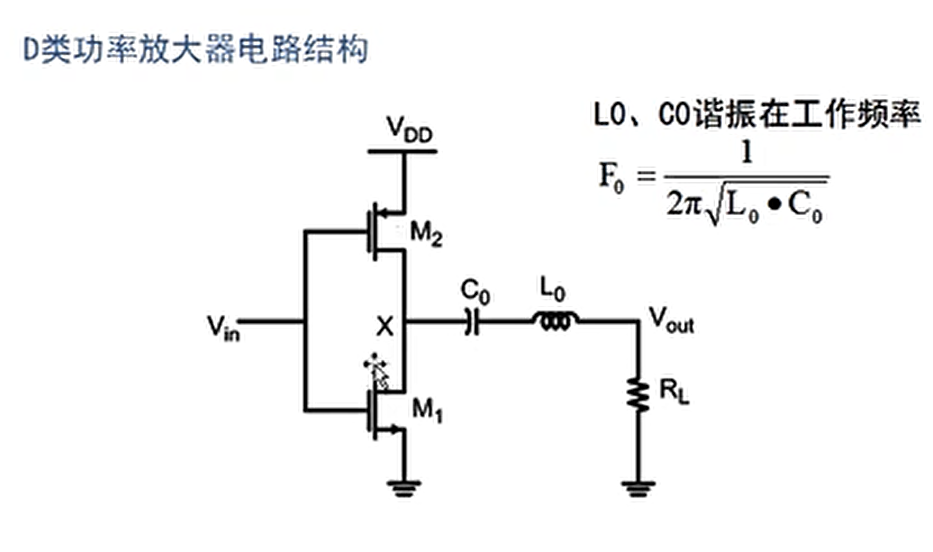

推挽输出,负载串联上串联谐振网络。(驱动电路被省略)希望输入信号的幅度越大越好,最好是

通常电感越大Q值越大,串联谐振网络的品质因数更好,选频特性越好。

但是还是要考虑电感的自谐振频率,要远远超过工作频率。

还要考虑工作带宽,比如80MHz,Q值太高会使得频带范围变窄----trade-off

JSSC 12 INVERSED CLASS-D AMP.

限制功率输出的因素包括,PMOS的导通阻抗以及负载阻抗(与此同时还要考虑电压摆幅的大小!)

在这里为了简化起见,直接将负载阻抗设置为50欧姆,以规避巴伦的使用。

在原理图当中,射频信号首先经过隔直电容。因为是2.5GHz的信号,所以取

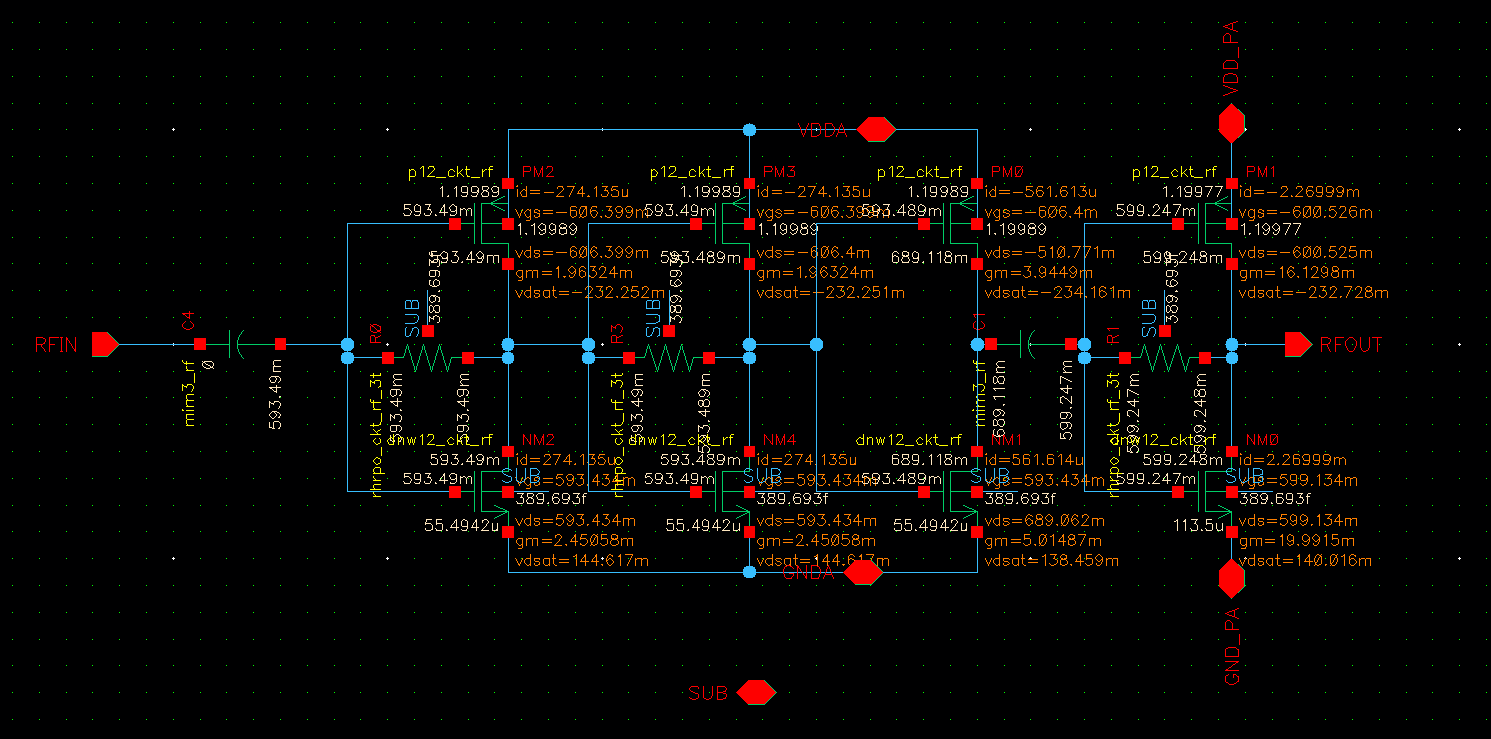

首先进行dc检查:

可以看到pmos和nmos的栅极电压约为

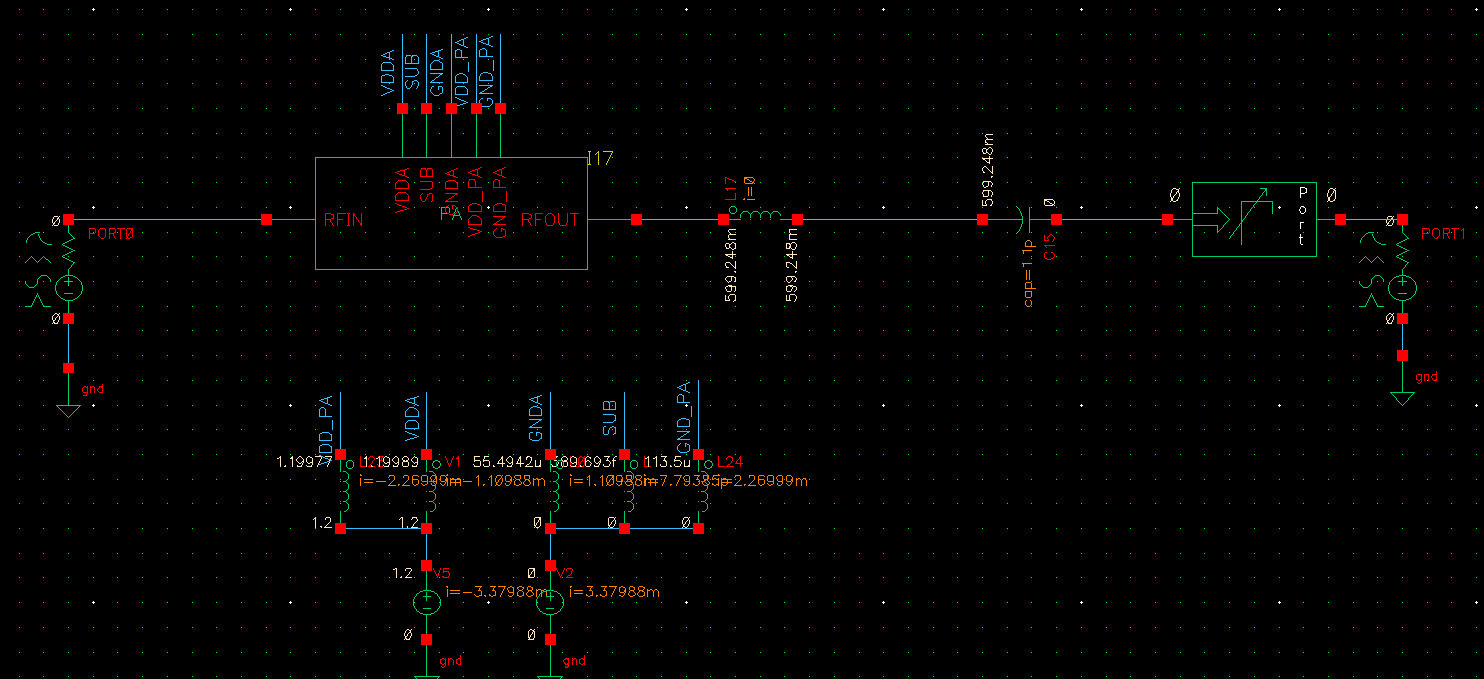

这里不关心输入匹配的部分,只需对输出进行匹配即可。通常我们认为输入端口的信号来自于上一级的VCO提供的

在这里使用2nH+100mΩ的理想电感以及100pH的理想电容分别充当引线电感和隔直电容:

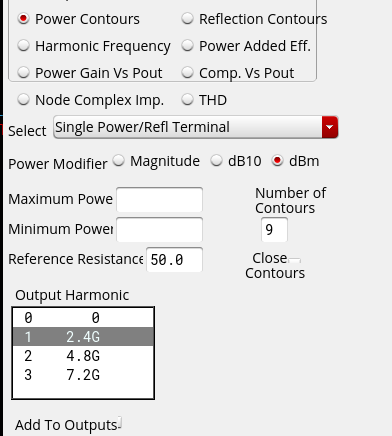

这里的PortAdapter由rfexample库给出:相位0-360°,幅度为0-1

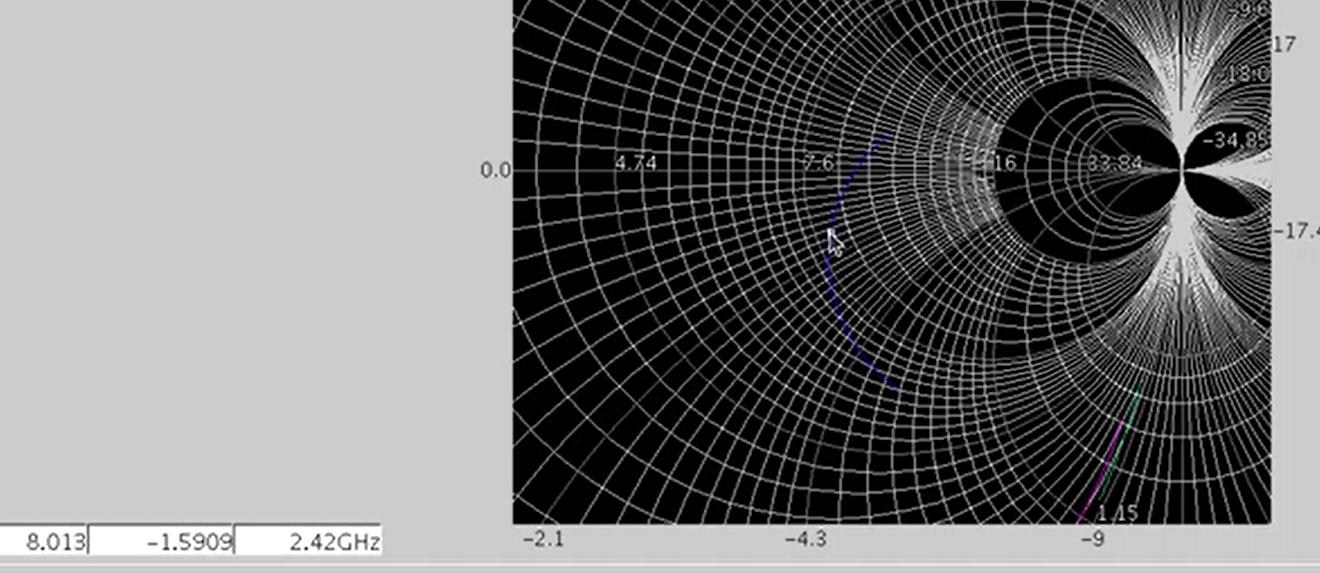

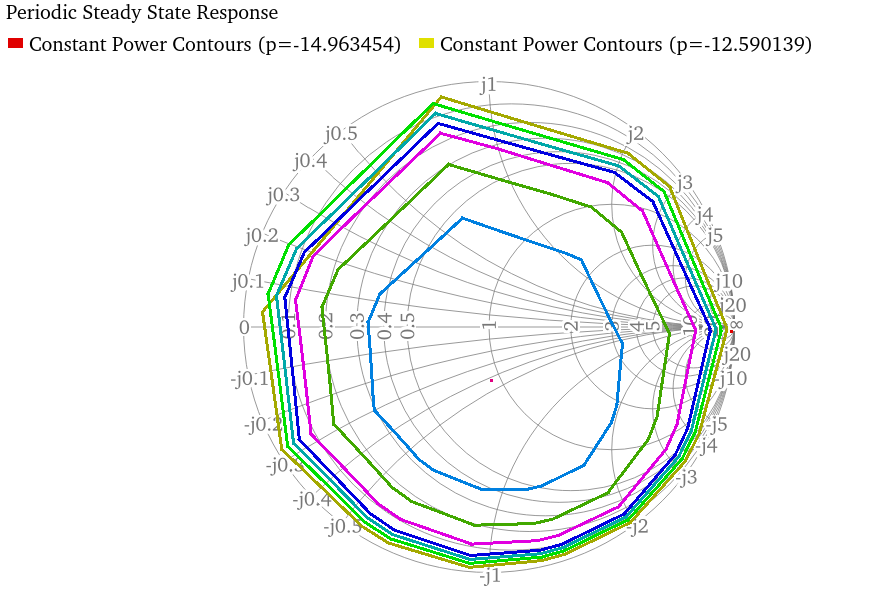

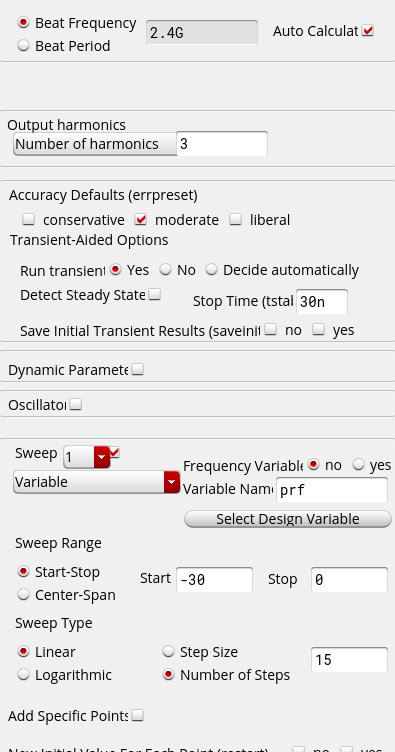

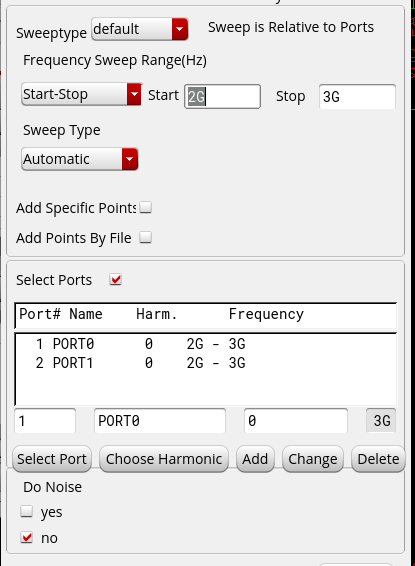

使用pss仿真,扫描相位和幅度。输出谐波1次谐波,作出9个闭合的圆得到闭合曲线

仿真结果大致这样(因为太慢所以步长给的很大,这里仅作参考)

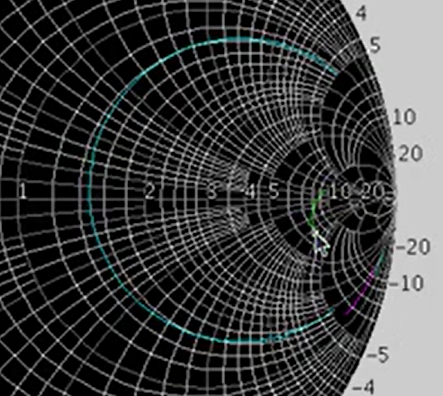

得到归一化的最佳阻抗为

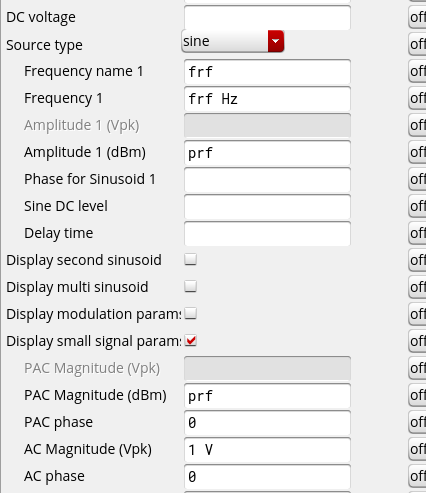

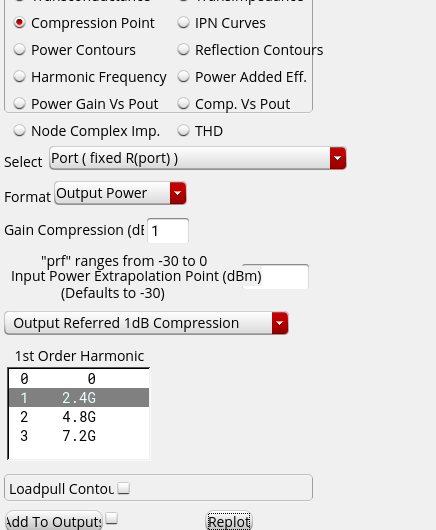

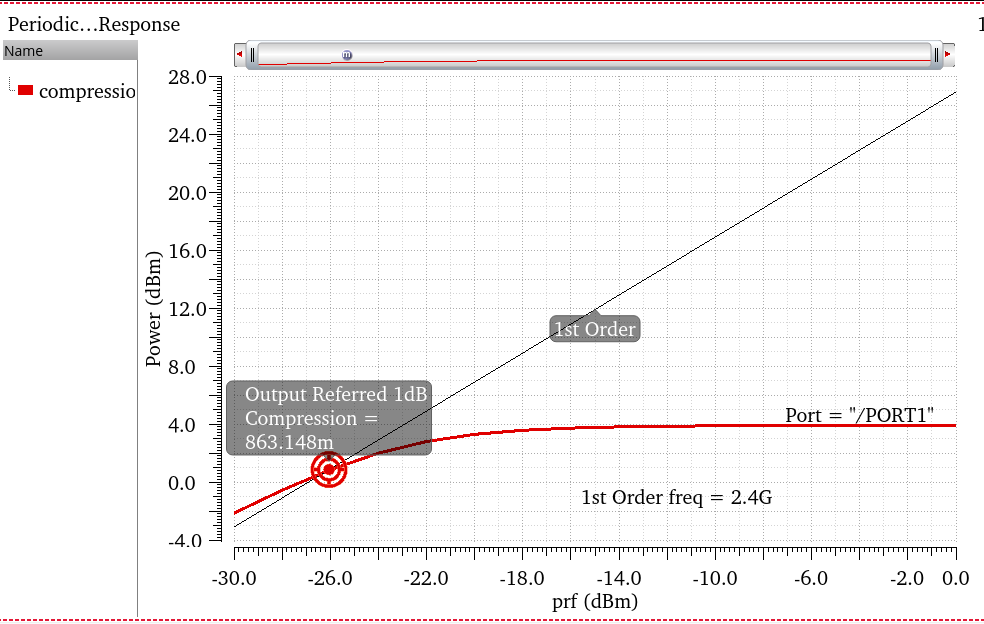

使用PSS对输入功率变量prf扫描得到1dB压缩点:

开关类的PA常工作于非线性,所以对非线性并不关心!

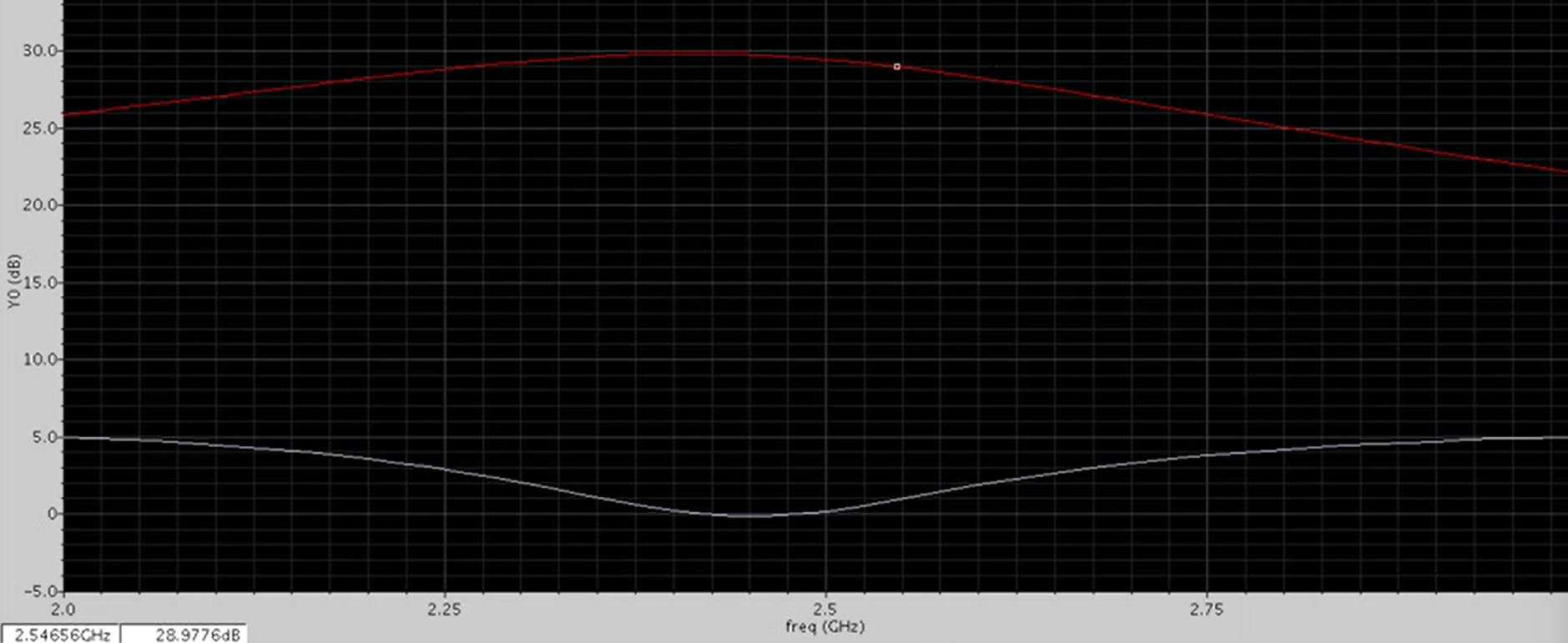

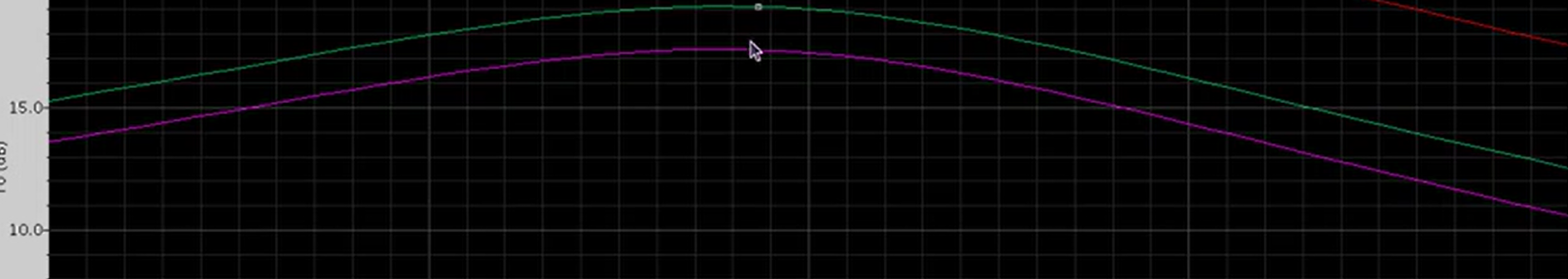

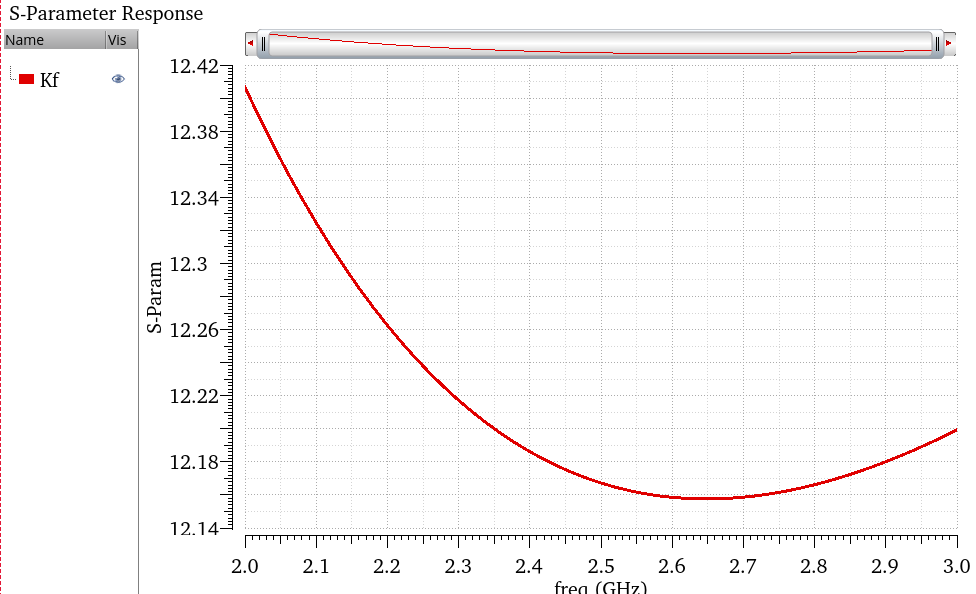

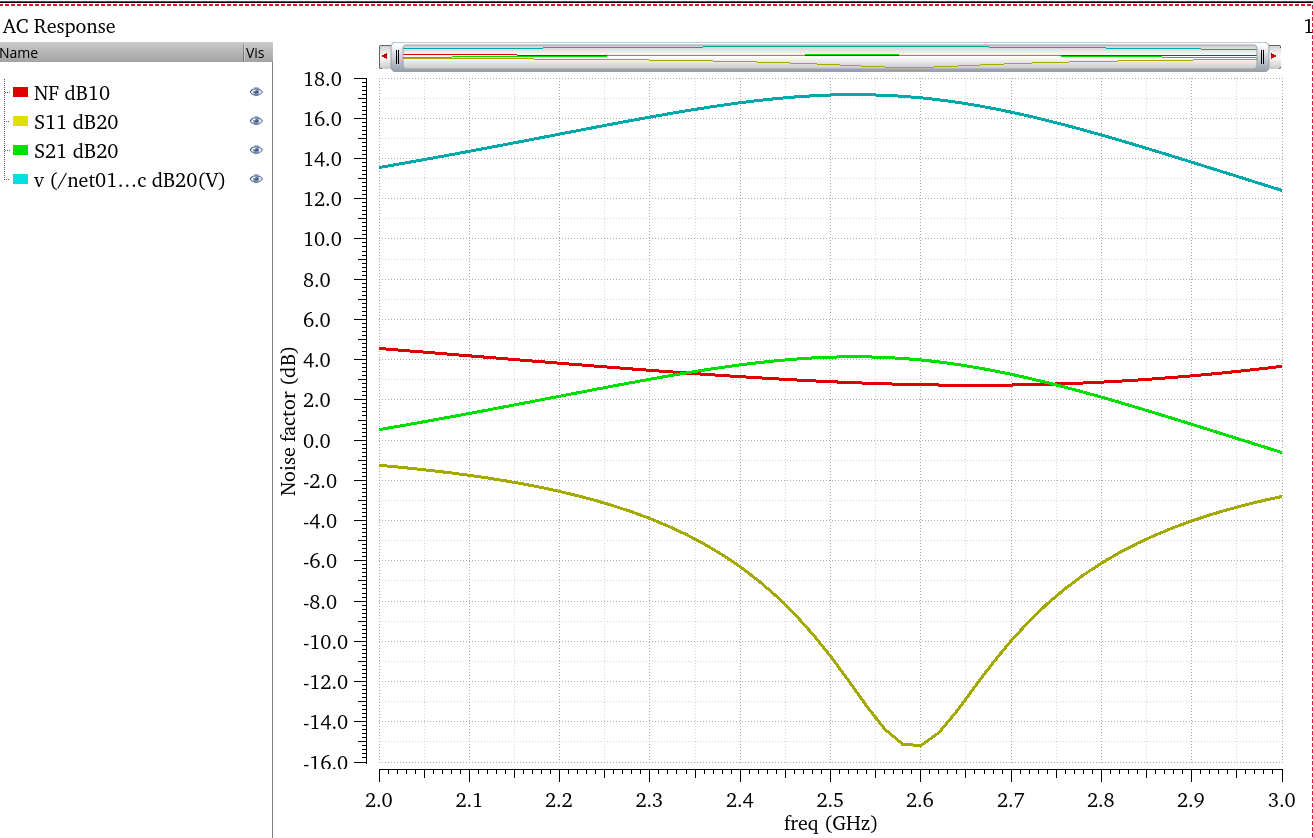

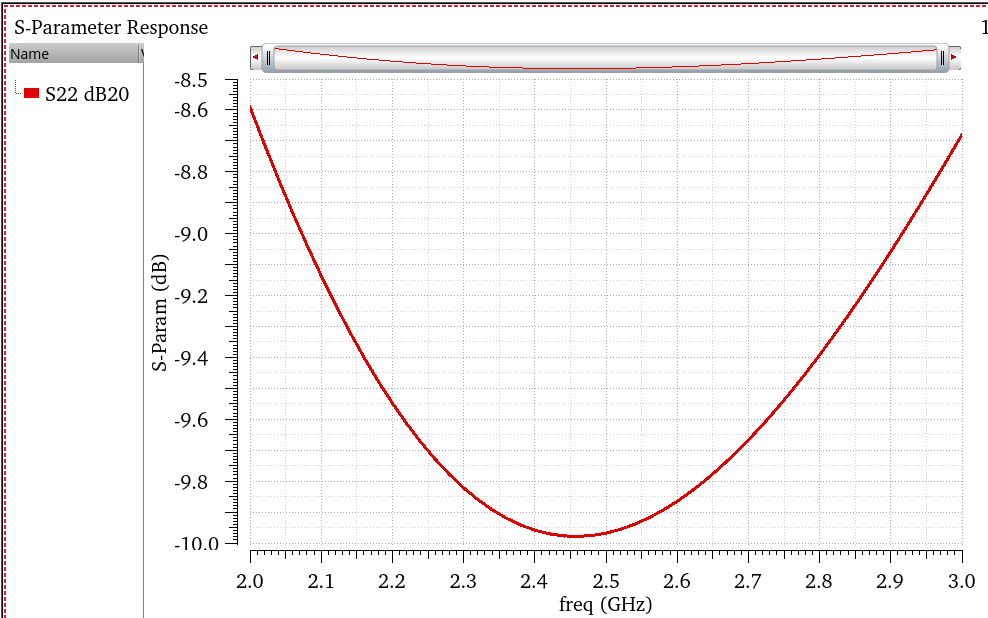

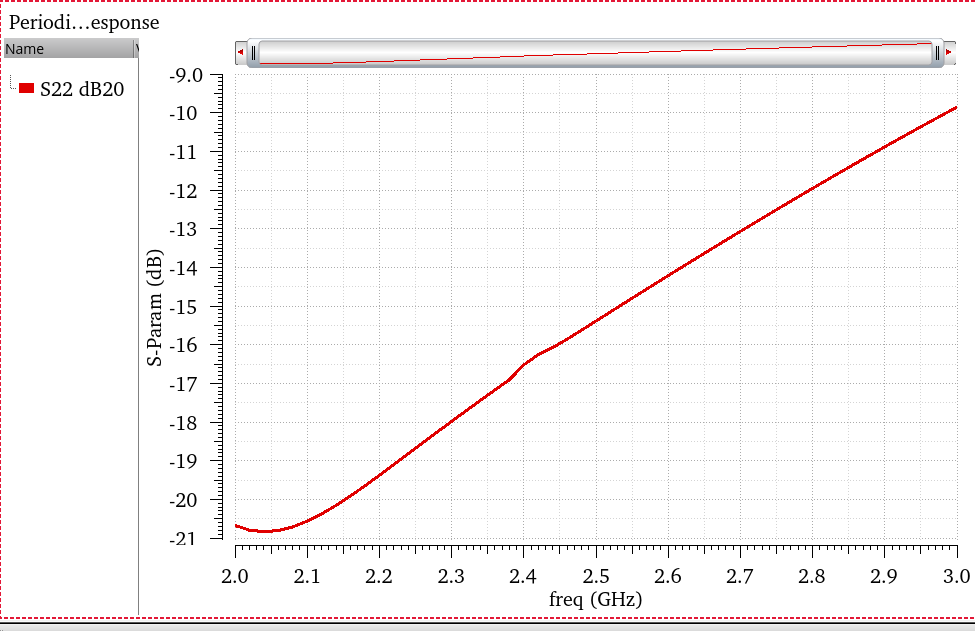

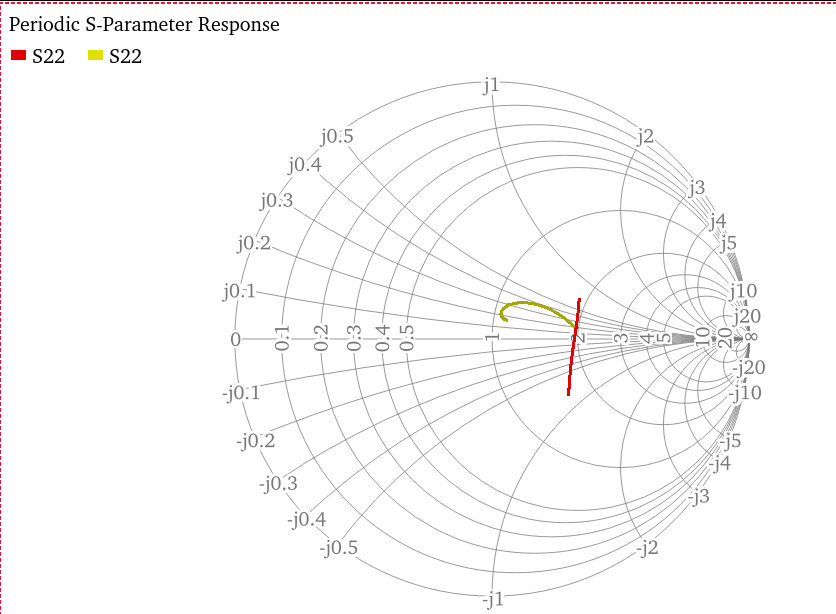

要注意S参数的分析是线性分析,但是在大信号状态下一般使用PSS+PSP分析,才能看出大信号下的阻抗匹配情况。psp仿真如下图所示:

如上图,上述的绿线是psp的结果,阻抗较小,而右侧的红线则是sp的结果,阻抗较大。

接下来仿真D类功率放大器:

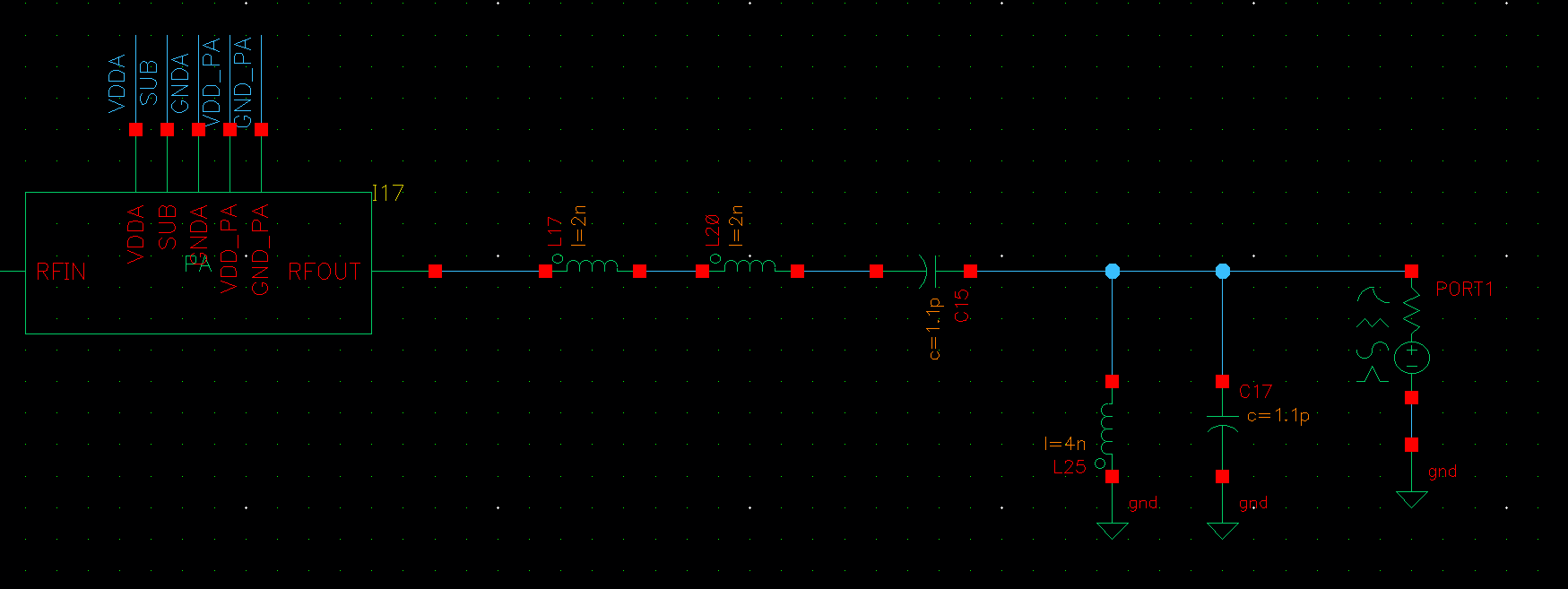

仿真的其它部分与之前的开关类放大器相同,但是这里的输出匹配网络使用4nH的电感以及1.1pF的电容构成第一级的串联谐振网络,并且将它们并联构成第二级的并联滤波网络进行输出方波的整形

首先使用sp仿真小信号进行输出匹配的仿真:

再使用pss+psp的大信号匹配状况:可以看到S22在2.4GHz<-15dB

下图(红色为小信号,黄色为大信号)可以看到大信号的匹配状况要更好一些。

通常认为大信号的匹配更能表现更为真实的状况。

调整输出晶体管级的尺寸,可以调整匹配情况。

输出1dB压缩点的情况,饱和输出功率(pss),瞬态波形(trans)

采用average( )函数可以计算电源输入功率

开关类PA的输出的谐波是很多的!

采用trans仿真后使用dft得到频谱,得到